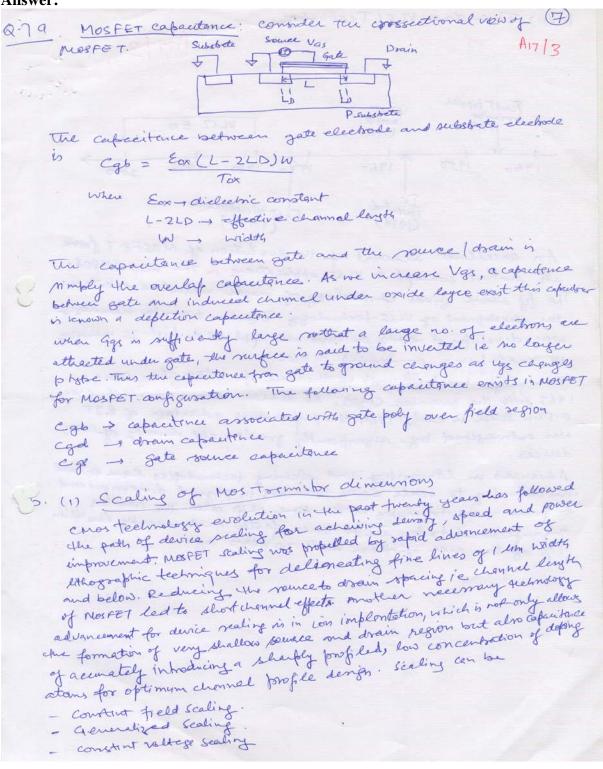

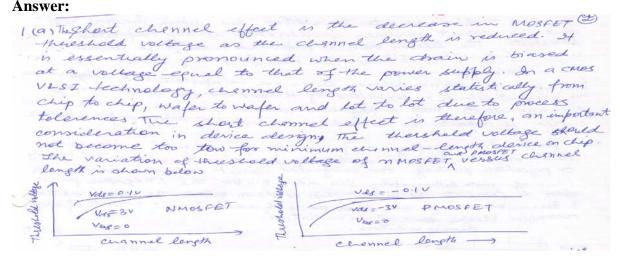

## 0.1a. Explain short channel effect in MOSFET.

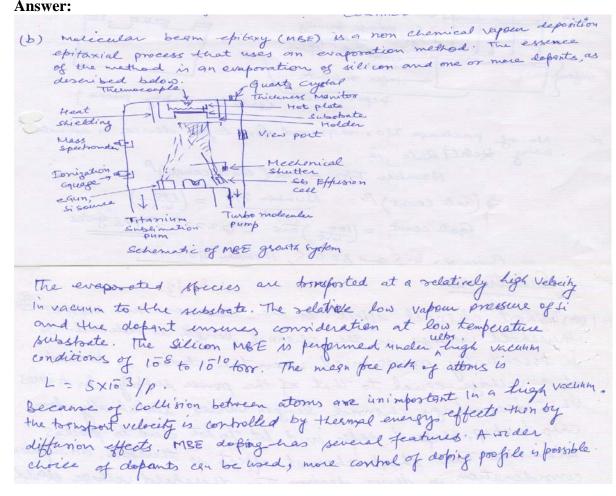

## b. Describe molecular beam epitaxy method to grow crystal.

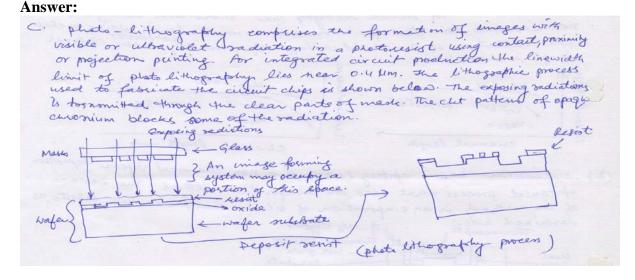

© IETE 1 c. Explain photo- lithography process to fabricate circuit chips.

d. Estimate the number of gates that can be included on a logic – gate array chip which is to be assembled in a 100 I/O package. Assume  $\alpha = 4.5$  and  $\beta = 0.5$

#### Answer:

```

package Ilos required for logic device is astimate

No of package 100 using Rest's Rule ie

Number 710 = & ( Gate count ) B

=> (Gate count) B = Number 7/0 = (100)

Gate court = (100 ) 0.5 = (22.22) = 493 gates

Biven 2 = 4.5 and B = 0.5, Number 70 = 100

```

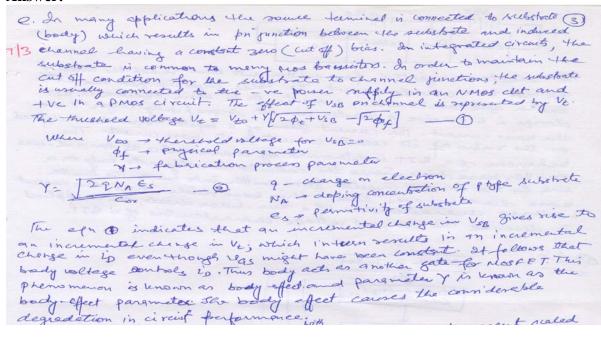

e. Explain body effect in MOSFET.

#### **Answer:**

#### f. Explain the effect of scaling on circuit parameters.

**Answer:**

f. Effect of circuit paremeters. Both vollage and whent realed down by some factor, the active chemnel resistance of the scaled down device remains unchanged. It is further arranged that parasitic sessistance is either negligible in scaling. The circuit delay, which is proportional to RC or CV/I then scales down by k. This, Once the device dimensions and power supply voltage are scaled down, the clet speeds up by some factor Moreover, power disripation per circuit, which is propostronal to VI, is reduced by k2. Since the circuit density has increased by k2, the power dinoity remains unchanged in the scaled down device. The pover-delay product of scaled coros circuit shows a dramatic improvement by a factor of k3 to and diades connected

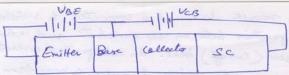

### g. Explain two PN diode model of BJT.

Answer:

J. PN diade model of BJT: BJT consists of two pN diades connected by operation improvement by a factor of Ks. back to back The basic operation of BIT can be described by operation back to back -diodes. To turn PNP tormistor on the emitter base diode is browned board is forward biased resulting in holes being injected from base into the emitter and electrons being injected from emitterito base. In normal oberation, base-called operation, base-collector diade is reverse bicsed to that there is no forward Edissent flow in the base - collectors diade. The bras condition and too

The electrons imjected from emitter into base reach the collector give now to a collector current. The holes injected from base into enritter give nise to a base current. On the basic objective in BST design is to acheive a calactor current signaficently larger than the base current. The current gain of a bipolar tramsfor is defined as the ratio of its collector current to its base current. The behaviour of a BIT is determined by characteristics of forward bias emitter base dide, Since the collector usually acts only as a sink for the carrier injected from emitter into base. The emitter like a thin base diade. Thus the carrent voltage characteristics of a thin-base diode con be applied to describe the current voltage characteristics of a BJT.

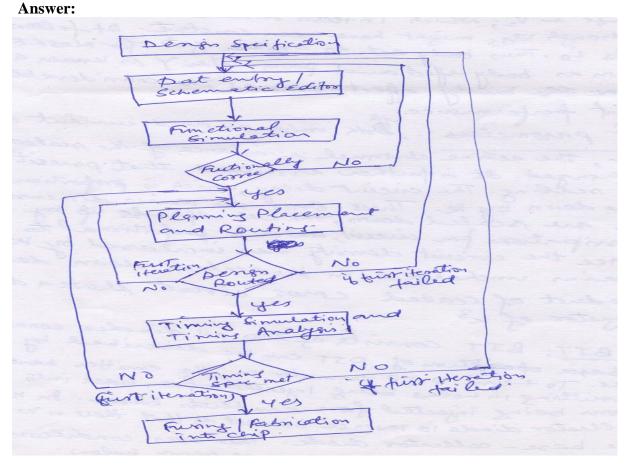

**Q.2** a. Explain VLSI design flow.

b. Give the comparison between CMOS and bipolar technologies. **Answer:**

| (b) Chas Technology  I low satatic power dissipation                                                                                 | Bipolar Technology A17/3                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 2. tigs IP impedence<br>3. Low drive current                                                                                         | 2. Low I/P impedence<br>3. high adrive current                                                                     |

| y. Scaleble threshold voltage Chigh noise margin  6. High packaging density  7 High delay sensitivity  8. Bidesectional Capabilities | 4. Sealable voltage 5. Low Valtage swing logic 6 Low partiaging density 7 Low delay sensitivity. 8 Unidirectional. |

| 9 low of Gmallin) 10 low of deine current                                                                                            | 4. high que md e'n) 10. high of p drive current.                                                                   |

4 © IETE

0.3 a. What is diffusion? Explain models of diffusion in solids.

Answer: Q:3(9) Diffusion: - Defusion mems to alter the type of conductivity in silicon or seemonium. Les process of inducing depent into silicon tog is known as diffusion. point defects known Models of diffusion. It high temperature, point defects known as diffusion. as vacancies and self interstitial atoms are severated in a single crueled single crystal rolid, when the concentration gradient of technot atoms are serviced to be atoms are serviced to be about the concentration gradient of the atoms in atoms eseists, such point defects affect atom movement. Defusion in polids can be visualized as atomic movement of diffusion in the cryptal lattice by vacancies. The fig below shows some common atomie diffusion models in a solid, Vacency using a simplified two 00/00 dimensional crystal Atmoture \_ 00 with lattice constant a. The oo oo o host atoms occupying low temperature latice positions. An interestiful atom moving from one place to quother place without occupying a lattice site is called interstitish diffusion mechanism. An atom smaller then host atom that does not form covalent bonds with silicon often moves intestitially. Fig (b) shows a 2 dimensional prichar of the atomic novement of a self interstitual atom displacing and impurity atom, which in turn becomes an interestial atom. Subsequently, the impurity atomasphaces another lost atom and the second host atom becomes a self intensitial. This is an example of extended interestitial meehonism. The vacancy and interestitially mechanisms are considered the doping mechanism for dopent impurity diffusion in silicom.

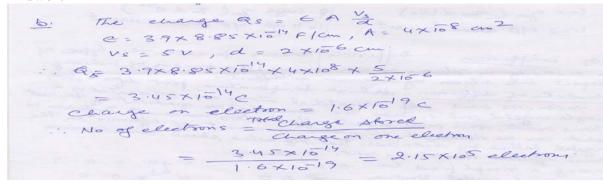

b. What is the stored charge and number of electrons on an MOS capacitor with an area of  $4\,\mu\text{m}^2$  a dielectric of 200 A° thick  $S_iO_2$  and applied voltage of 5V?

Answer:

Q.4 a. How VHDL is used to model the digital. Answer:

| that he                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G.4 (9) VHOL is a hardware description longuage that be used to model a digital system st provides five different types of primary constructs, called deorgn units; they are - Entity deduration - Architecture body - configuration declaration - Package declaration - Package body:                                                                                                            |

| An entity is modeled using an entity declaration and at (5) least one architecture body. The entity declaration describes H17/3, the external view of the Centity.                                                                                                                                                                                                                                |

| least one architecture body. The entity declaration describes the external view of the centity.  The architectural body contains the internal description of the entity for example, a set of interconnected components that represents the structure of the entity or as a set of concurrent or sequential the structure of the entity or as a set of concurrent or sequential                   |

| of sepresentation can be specified in a different body.  of sepresentation can be specified in a different body.  of sepresentation can be specified in a different body.                                                                                                                                                                                                                         |

| for an entity. It specifies the bindings of components used from many architectures bodies that may be arrowed used                                                                                                                                                                                                                                                                               |

| in the selected architecture body to other evantions.  in the selected architecture of different configurations.  may have any number of different configurations and pubprogram  A package declaration encapsulates a set of related declaration  and pubprogram  mely as type declarations, subtype declarations and pubprogram  mely as type declarations, subtype declarations and pubprogram |

| met as type declarations, suisified across the declarations which can be shared across of subsprograms declared declarations which can be shared across of subsprograms declared                                                                                                                                                                                                                  |

| much as type declarations, subspice the across two of subsprograms declared declarations which can be shared across of subsprograms declared units.  A package body contains the definitions of subsprograms declared in a package declaration.  In a package declaration.                                                                                                                        |

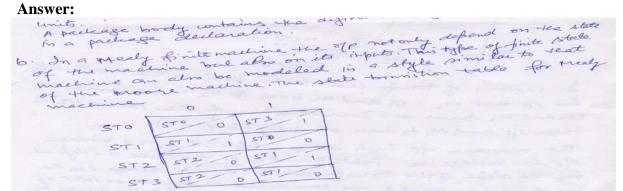

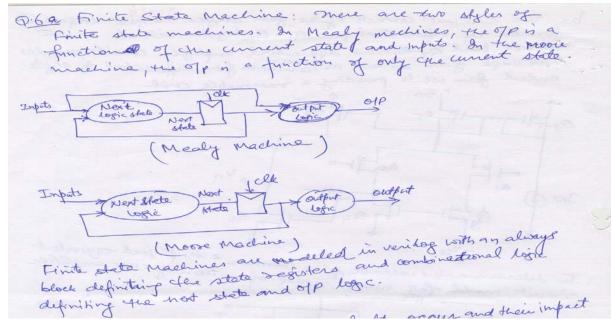

b. Give state transition table for Mealy machine.

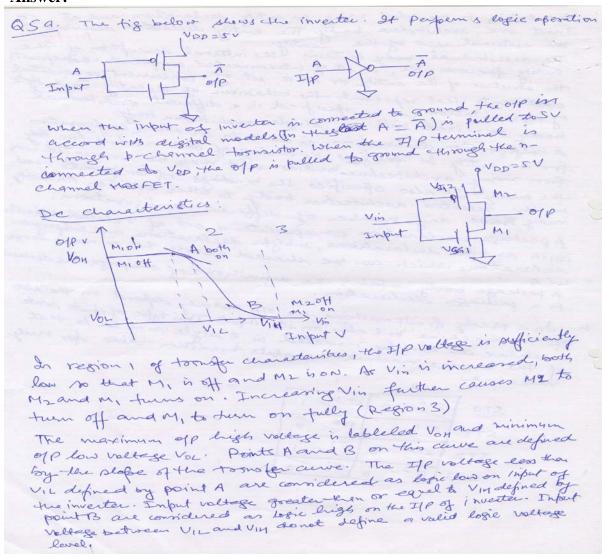

#### **Q.5**

a. Draw the block diagram of a general two-stage op-amp and explain the working operation of each block.

#### **Answer:**

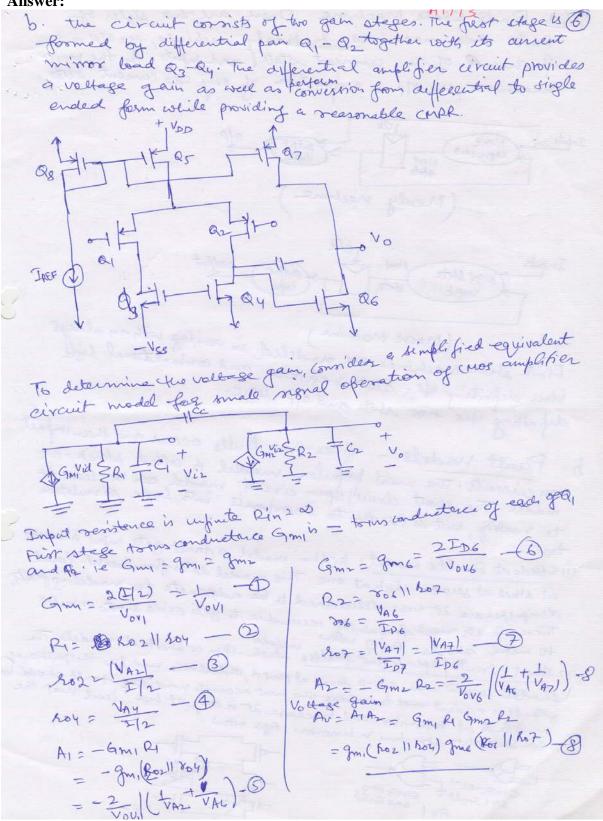

#### b. Draw the two stage CMOS OPAMP Configuration and calculate its voltage gain. Answer:

8 © IETE

#### 0.6 a. Explain finite state machines.

#### Answer:

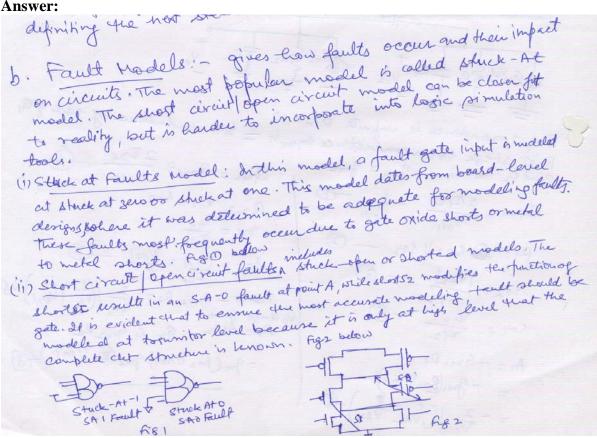

#### b. Explain fault model in VLSI design.

# Q.7 a. Explain the importance of scaling of MOS transistor dimensions. Explain the types of scaling and show the effects of parameters in constant voltage scaling. Answer: