Q.2 a. Perform the following conversions:

(i)

$$(735)_8 = (?)_2$$

**(ii)**

$$(37FD)_{16} = (?)_{10}$$

**(iii)**

$$(37.45)_{10} = (?)_2$$

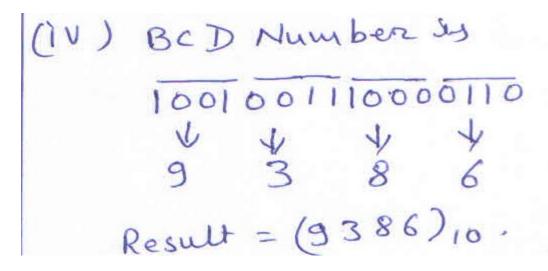

(iv) BCD number 1001001110000110 in to its decimal equivalent.

#### **Answer:**

(i)

$$(735)_8 = (?)_2$$

$735$

$111 \ 011 \ 101$

$\therefore [(735)_8 = (111011101)]$

(ii)  $(37FD)_{16} = (?)_{10}$

$\Rightarrow (3 \times 16^3) + (7 \times 16^2) + (15 \times 16^1) + (13 \times 16^0)$

$\Rightarrow (12288 + 1792 + 240 + 13)$

$\Rightarrow (14333)$

$\Rightarrow (14333)$

$$\frac{2}{37}$$

$$\frac{2}{37}$$

$$\frac{2}{18}$$

$$\frac{2}{9}$$

$$\frac{2}{9}$$

$$\frac{2}{9}$$

$$\frac{2}{9}$$

$$\frac{2}{10}$$

$$\frac{$$

b. Define binary system.

**(2)**

**Answer:**

Binary system!

In the binary system there are only two symbols or possible digit values, O and I. This base-2 system can be used to represent any quantily that can be represented in dicinal or other number system. In binary system, the term binary digit is often abbreviated to the term binary digit is often abbreviated to the term bit.

c. What are advantages and limitations of digital system over analog system? (6) Answer:

Advantages of Digital System

(1) Digital system are generally easier to design

(2) Information storage is easy

(3) Accuracy and Precision are greater.

(4) Operation can be programmed.

(5) Digital circuits are less affected by Noise.

(6) More digetal circuitry can be fabricated on Ic chips.

Limitation

(1) The real world is mainly Anolog.

2

0.3a. What do you mean by universal gate? Implement AND, OR and NOT gate using any one of universal gate.

#### **Answer:**

Universal gate: The "NAND" operation and "NOR" operation have become very popular and are widely used, the reason being that only one type of gates, exther NAND or NOR are sufficient for realization of any logical expression. Because of this reason, NAND and NOR gates are known as Universal getes. Realization of gates by using NAND gate (i) NOT gate (ii) AND gate Y= AB = AB Viii) OR gate  $Y = \overline{A \cdot B} = \overline{A} + \overline{B} = A + B$

b. Simplify the following expression, construct the corresponding logic circuit using basic gates. (6)

Y = A + BC + ABC + ABC

Given

$$Y = A + \overline{B}C + ABC + A\overline{B}C$$

$Y = A + \overline{B}C(A+1) + ABC$

$Y = A + \overline{B}C + ABC$

$Y = \overline{B}C + A(1+BC) = \overline{B}C + \overline{A}C$

c. Draw the symbol of XNOR gate and explain its working with the help of truth table. (5)

#### **Answer:**

Exclusive-NOR gate !- XNOR gate

This gate has two supputs and one output. In

Ex-NOR gate, the output is high when both

Ex-NOR gate, the output is high when both

inputs are high, other wise output is low. A

inputs are high, other wise output is given below

truth table and logic symbol is given below

| A | В | 7 |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$\begin{array}{c} \overline{A}B + A\overline{B} \\ B \end{array}$$

Q.4a. Perform the following operations:

**(8)**

- (i) Subtract -36 from 15 using 2's complement.

- (ii) Add 623 and 599 using BCD code.

Answer:

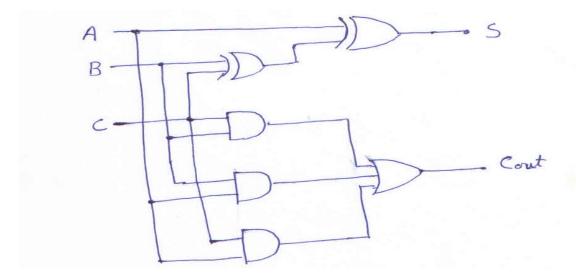

b. Design and explain full adder circuit using truth table. (8) Answer:

Design of Full Adder

Truth table of Full Adder is

| A | В   | cin | Sum | Carry |

|---|-----|-----|-----|-------|

| 0 | 0   | 0   | 0   | 0     |

| 0 | 0   | 1   | 1 1 | 0     |

| 0 | 1.  | 0   | 1   | 1 1   |

| 0 | 1   | 1   | 10  | 10    |

| 1 | 0   | 0   | 0   | 1     |

| 1 | 0   | 11  | 0   | 1 1   |

| , | 1 , | 10  | 11  |       |

Truth table howing three Inputs A, B, ein and two outputs S and Cout. There are eight possible cases for the three inputs, and for each case the desired output values are listed.

Since there are Iwo outputs, we will design the circuitry for each oritput individually. For s, the truth table shows that there are four cases where s=1.

Using SOP method, expression for SJ

S= ABCin+ ABCin+ ABCin+ ABCin

OR S = A (Bain+Bain) + A (Bain + Ban)

OS S = A (B + Cin) + A (B+ Cin)

If we let X= B @ Cin, then

$S = \overline{A}X + A\overline{X} = A \oplus X$

Replacing X, we have

S=AD[BOCIN] - --- (D)

Similary SOP for cont

Cout = AB Cin + AB Cin + AB Cin + AB Cin

= BCin (A+A) + Acin (B+B) + AB( CIN+CIN)

=BCin + Acin + AB. - -- 2

This expression cannot be simplified further. Expression @ and @ can be implemented as shown in figur below.

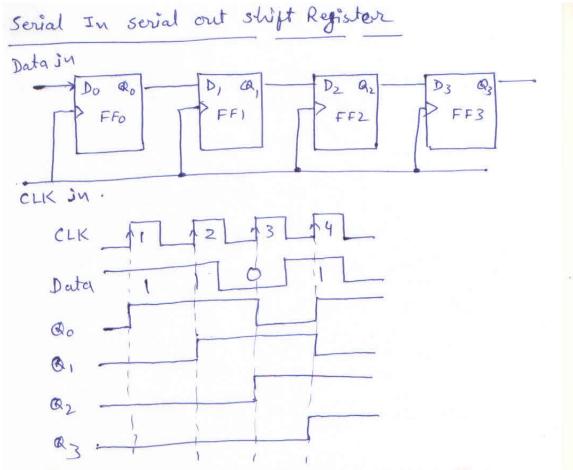

Q.5 a. Draw the circuit of 4 bit serial in serial out shift register and explain its working. (8)

Figur shows a 4 bit serial in social out stipt register consisting of four D flop flops FF0, FF1, FF2, FF3. As shown it is positive edge triggered device. We study the working of this register for the data 1010 in the following Steps.

- 1. Bit O is entered in to data input line Do=0, first clock pulse is applied. FFo is reset and stores O.

- 2. Next but 1 is entered Qoco, Since Qois connected to D1, D1 becomes O.

- 3. Second clock pulse Is applied. The I on the input line is shifted into FFO, The O'was stored in FFO is shifted into FFI

- 4. Next bit a is entered and 3rd clock pulse applied. O' is entered into FFO, it stored in FFO is shipted to FFO and o'stored in FFO is shipted to FFO.

- 5. Last bit I is entered and 4th clock pulse applied. I' entered in FFO, 'O'stored in FFO is shifted to FFI, I' stored in FF, is shifted to FF2 and 'O'stored in FF2 is shifted to FF3. This completes the serial entry of is shifted to FF3. This completes the serial entry of 4 bit data into the register. Now LSB 'O' is on the output O3.

- 6. 5th clock pulse is Applied, LSB 'O'is shifted out. The next bit'i appears on Q3 output.

- 7. 6th clock pulse is applied, the I'on Q3 is shipted out and o'appears on Q3 output.

- 8. 7th clock pulse is applied, o'one as is shifted out Now i'appears on as output.

- 9. 8th clock pulse is applied, i (one) an Qz is shipted out. when the bits are being shipted out, more date buts can be entered in

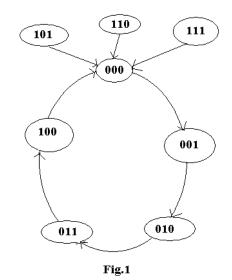

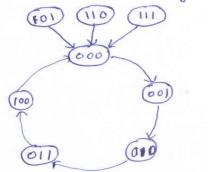

- b. Explain design procedure to design synchronous counter whose state transition diagram is shown in Fig.1. (8)

Given state transition diagram is

Step 1! - Determine the desired number of bits (FFs) and the desired counting sequence.

Step 2! - From the state transition diagram set up a table that tist all "present" states and their Next' states.

Table shown below shows Present state and Next state.

|       | Pho | seut | stat | e | , , | vesit: | state |   |

|-------|-----|------|------|---|-----|--------|-------|---|

| Line. | C   | B    | A    |   | c   | В      | A     |   |

| t     | 0   | 0    | 0    |   | 0   | 0      | 1     |   |

| 2     | 0   | 0    | - 1  |   | 0   | 1      | 0     |   |

| 3     | 0   | 1    | 0    |   | 0   | 1      | 1     |   |

| 4     | 0   | 1    | 1    |   | 1   | 0      | 0     |   |

| 5     | 1   | 0    | 0    |   | 0   | 0      | 0     |   |

| 6     | 1   | 0    | 1    |   | 0   | 0      | 0     |   |

| 7     | 1   | . 1  | 0    |   | 0   | 0      | 0     | 1 |

| 8     | 1   | 1    | 1    |   | 0   | 0      | 0     |   |

© iete

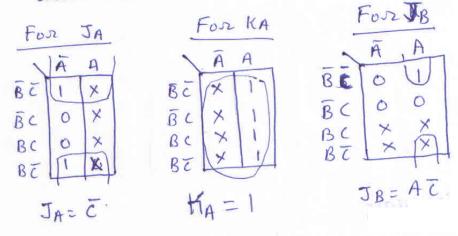

Step 3: - Add a column to this table for each Jand K input. For each Present state inclicate the levels required at each Jand K input in order to produce the transistion to the next state.

| Line - | Drusent   State   C B A   O O O O O O O O O O O O O O O O O O | Nextate.  C B A  O O I  O I O  O O O  O O O  O O O | 1.7 | Ke * * * * 1 1 1 1 | 2B 0 1 X X 0 0 X X | KB X X O 1 X X 1 1 | JA<br>1×1×0×0× | KA<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X |  |

|--------|---------------------------------------------------------------|----------------------------------------------------|-----|--------------------|--------------------|--------------------|----------------|-------------------------------------------------|--|

|--------|---------------------------------------------------------------|----------------------------------------------------|-----|--------------------|--------------------|--------------------|----------------|-------------------------------------------------|--|

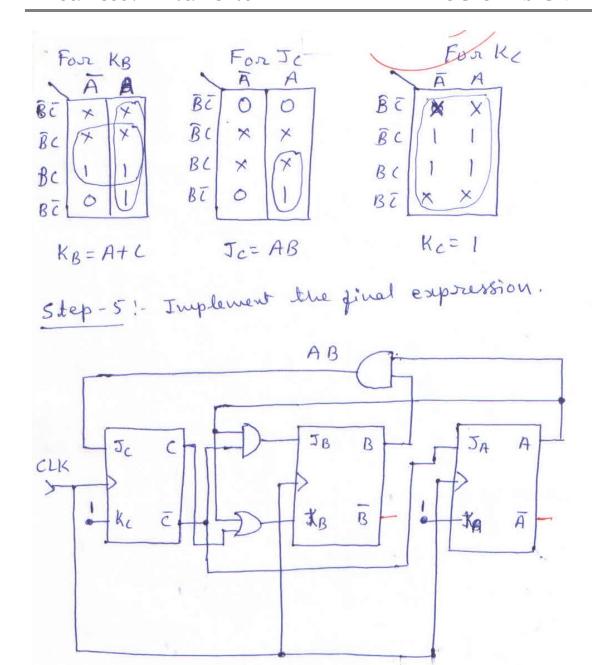

Step 4! - Design the logic circuits to generate the levels required at each J and K suput.

Solve JA, KA, JB, Jc, RB, Kc Using K-map from above table.

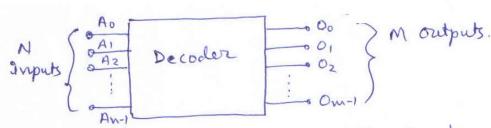

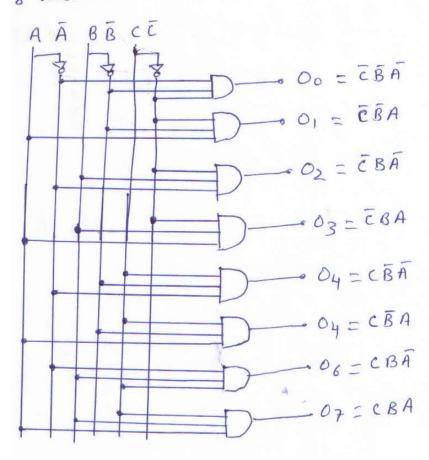

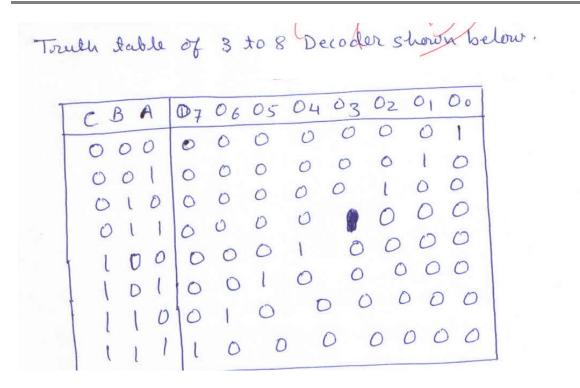

a. What is decoder? Explain working of a 3 to 8 line decoder with the help of its **Q.6** detailed logic diagram and truth table. **(8)**

Decoders! - A decoder is a logic carcuit that accepts a set of inputs that represents a binary number and activates only the output that corresponds to that input number. Figur shows Block dragram of General decoder,

For N inputs, there are m= 2 N outputs.

Figur shows below the circuitry of four a decoder with three inputs and  $2^3 = 8$  outputs. It uses all AND with three inputs and active HIGH. Note that gates, and so the outputs are active HIGH. Note that you for a given input code, the only output that is advers for a given input code, the only output that is adversed to the one corresponding to the decimal equivalent of the binary input code. It can be called a 3 to 8 decoder.

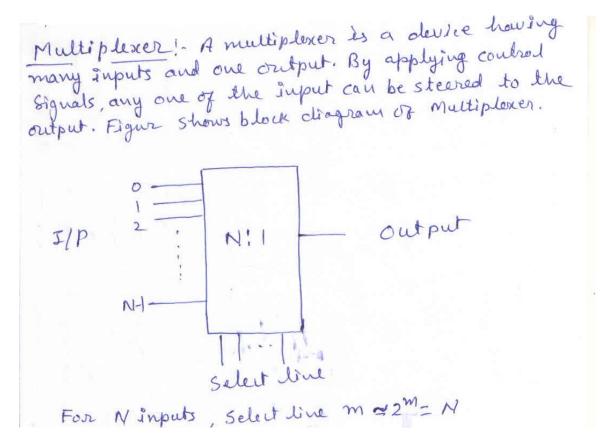

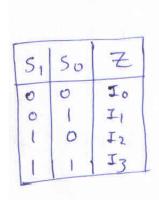

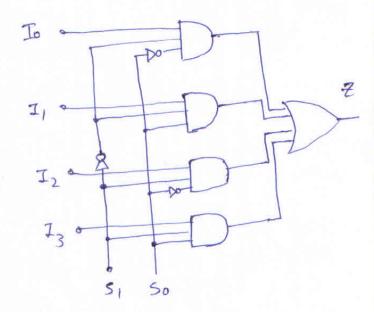

b. What is multiplexer? Draw logic diagram of four inputs multiplexer and explain its working. (8)

Four. Input Multiplexer!

Figur shown below a multiplexer with 4 inputs and 2

data select lives. A two binary code on the data

select inputs allows the corresponding data to appear

at output Y. The data input lives are Io, I, I, I, I and

select lives as Sofis. The data selection is shown

In the truth table.

It is clear that when  $S_0=0$ ,  $S_1=0$ ,  $Z=T_0$ .  $Z=T_0$ ,  $Z=T_0$  when  $S_0=0$ ,  $S_0=0$ ,  $Z=T_1$ .  $Z=T_1$ ,  $Z=T_1$ ,  $Z=T_2$ ,  $Z=T_3$ , Z=

Q.7 a. Draw the logic diagram of JK flip flop and explain its working using truth table. (6)

Answer:

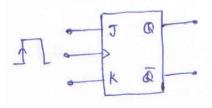

| Т  | IK | CLK | Ca   | Remark   |

|----|----|-----|------|----------|

| 0  | 0  | 1   | Qo   | Nochange |

| 1  | 0  | 4   | 1    | Set      |

| 0  | 1  | 41  | 0    | Toggles  |

| 11 | 1  | 14  | Colo | 1000     |

The truth Jable of JK flip flop Is shown In figur above. The operation of this FF is shown by the wave form in figur above. Working of flip flop can be explained in the following stops.

1) Initially all Inputs are o and the of output its assumed to be 1; that is do = 1

(2) when the positive going edge of the first clock pulse occurs, the J=0, and K=1, condition exists. Thus FF will be cleared to the Q=0 state

3 The second clock pulse finds J= K= 1, when it waky its positive transition. This cause the IFF to loggle to its opposite state, i.e. Que!

- A Next clock pulse finds J=k=0, so that the FF does not change states on this transition.

(5) During next clock pulse, J=1, K=0. This is the condition that sets of ito the 1's tate. However it is already 1, and so it will remain there.

(6) During next clock pulse transition, J=K=1, and (7) During next clock pulse transition, J=K=1, and (8) Note that from these wave forms that the FF is not affected by the negative going edge of the clock pulse.

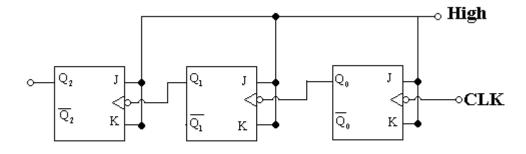

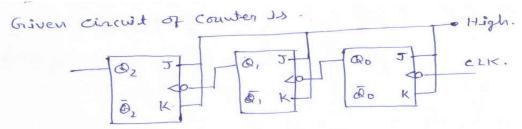

- b. Consider the circuit shown in Fig.2, (10)

Fig.2

- (i) Determine the counter's MOD number

- (ii) Determine the frequency at the output of the last FF (Q2) when the input clock frequency is 1MHz.

- (iii) What is the range of counting state for this counter?

- (iv) Assume starting state is 000. What will be the counter's state after 129 pulses?

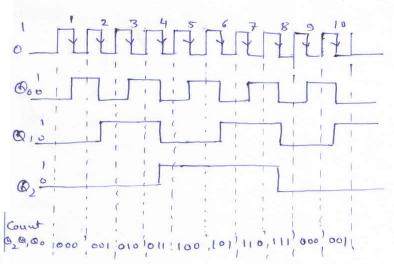

- (v) Draw waveforms at  $Q_0, Q_1, and, Q_2$  for the 10 input clock pulses.

- (a) MOD Number! -MOD Number = 23 = 8

- (b) The Engineery of lost Flip floop will equal the supert clock frequency divided by MOD number. That is  $f(at a_2) = \frac{1MH_3}{8} = 125 KH_3.$

- (C) The counter will be count from 000 to 111 for a total of 8 states. Note that the number of states is the same as the mode mode number.

- (d. Since this is a MOD-8 counter, every 8 clock pulses will bring the counter back to its starting state.

There-fore, after 128 pulses the count is back to ooo. The 129th pulse bring the counter to the ool counter.

- (e) waveforms at Qo, Q1, Q2 is shown below for 10 input clock pulses.

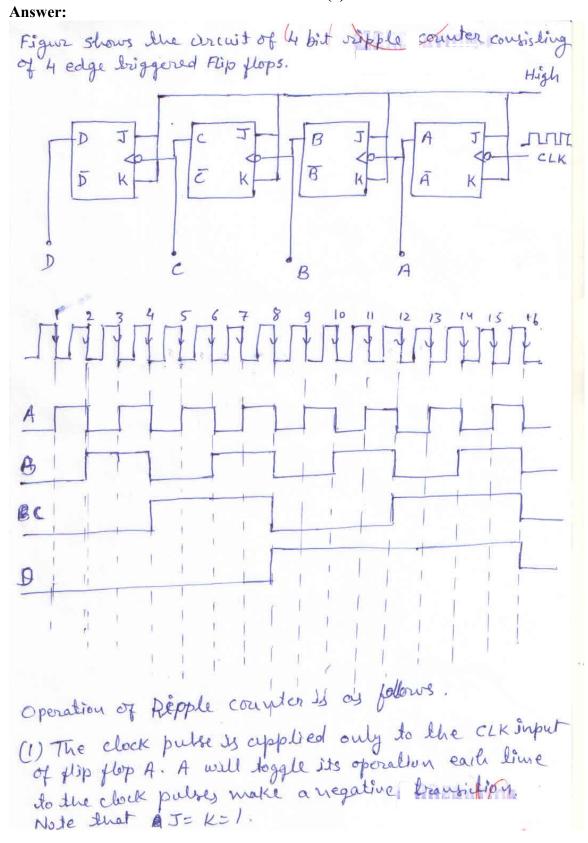

Q.8 a. Explain working principle of ripple counter with suitable logic diagram.

(8)

- (2) The normal output of flip flop A acts as the CLK Imput for thip flop B, and so flip flop B will toggle each time the A output goes from 1 to 0. Similarly flip-flop c will toggle when Bgoes from 1 too, and flip flop D will toggle when c goes from 1 to 0. (3) FF outputs D, C, B and A represents a four but binary number with D of the MSB. Lets assume that all FFs have been cleared to the 'o'state. The wave form shown that binary sequence of counting from 0000 to 1111 is followed as clock pulses are continuosly applied. (4) After the NGT (negative Trigger) of the fifteenth clock pulse has occurred, the counter FFs are in the IIII condition. On the sixteenth NGT, flip flops A goes from 1 too, which causes flip flop B goes from 1 to0, and so on, until the counter is in the oood state. This type of counting arrangement is alled Asynchronory counter.

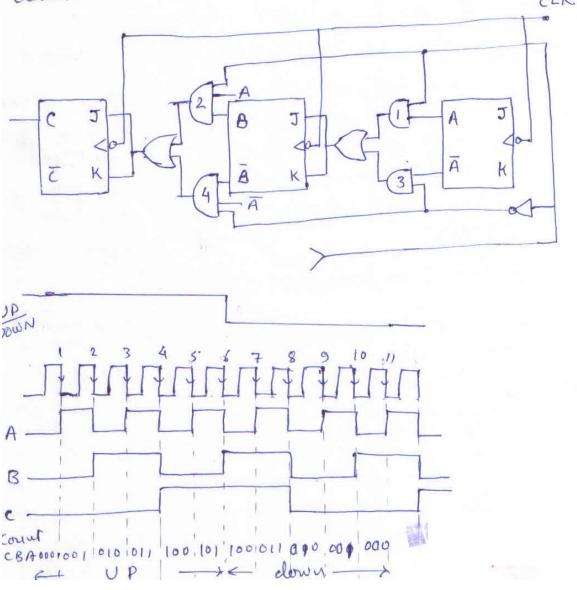

- b. Design a mod 8 synchronous up/down counter and explain its working with the help of timing wave form. (8)

Figur shows a parallel up clown counter. The control input UP/DOWN controls whether the normal FF outputs or the inverted FF outputs are fed to the J and K inputs of the successive FFs. When UP/DOWN is held HIGH, AND gates I & 2 are enabled while AND gates 3 and 4 are disabled. This allows the A and B outputs through gates I and 2 to the J,K inputs of FFs B and

When UP/DOWN Is held LOW, AND gates 1 and 2 are disabled while AND gates 3 and 4 are enabled. This allows the A and B outputs through gate 3 and 4 into the J and K inputs of FFs B&C. The The were forms in the given figure illustrate the operation. Notice that for the first five clock pulses, UP/DIDWN = 1 and the counter count up; for the last five pulses, UP/DOWN = 0, and the counter counts down.

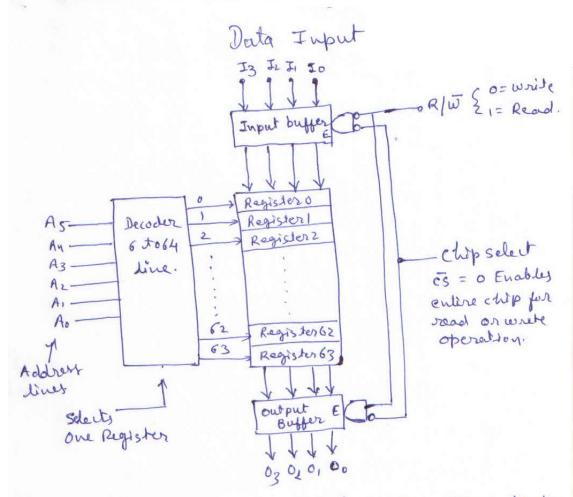

Q.9 a. Explain with neat diagrams RAM architecture.

**(8)**

Figur shows simplified architecture of a RAM that stores 64 words of four bit each. These word have addresses ranging from 0 to 63. In order to select one of the 64 address locations for reading or writing, a binary address code is applied to a decoder chrewit. Since 64 \$26 the decoder requires 6 bit Input code. Each address code activates one particular decoder output, which, in term enable its co-versponding register. For example, assume an applied todards code of

A5 A4 A3 A2 A, A0= 011010

Since 011010 = 26, decoder output 26 will go high, register 26 selected for either read our a write operation.

Read operation! - In order to read the contents of the selected register, the READ/WRITE (R/W) input must be I and c3 input must be activated.

While operation! - For white operation R/W=0 and c5 = 0.

where c5 = chip select imput which used to earable the entire chip or disable it completely.

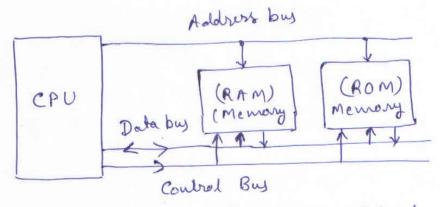

b. Describe CPU – Memory connection with suitable block diagram. (8) Answer:

A computer's main memory is made up of RAM and ROM. that are interfaced to the CPU over three groups of signal line or buses, called Address bus, data bus and control bus as shown in figur.

whenever the CPU wants to write data to a particular memory location, the following steps must occur.

## Mirite Operation

- 1. The CPU supplies the binary address of memory location where the data are to be stored. It places this address on the address by Muy.

- 2. The CPU places the data to be stored on the data bus lines.

- 3. The CPU activates the appropriate control signal lines for the memory write operations.

- 4. The memory decode the binary address to determine which location is being selected for the store operation.

- 5. The data on the data bus are transferred to the selected memory location.

# Read Operation!

- 1. The CPU supplies the binary address of the memory location from which data are to be retrieved. It places this address on the address bus lines.

- 2. The cpu activates the appropriate control signal for the memory read operation.

- 3. The memory Ics decode the binary address to determine which tocalion is being selected for the read operation.

- 4. The memory Ics place data from the selected memory location on to the data buy, from watsets they are draw ferred to the CPU.

#### TEXT BOOK

Digital Systems - Principles and Applications, Ronald J Tocci, Neal S. Wildmer, Gregory L. Moss, Ninth Edition, Pearson Education, 2008