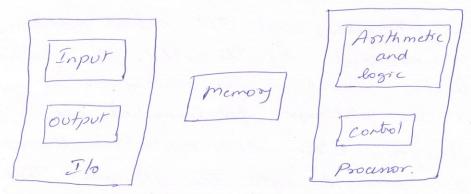

Q.2 a. Explain basic functional units of a computer with the help of neat block diagram. (8) Answer:

A computer consists of five functionally independent main parts: (1) inpot (2) memory (3) Arithmetic (4) output and logic (5) control units as shown in the diagram.

<u>Input</u>: This unit accepts coded information from human operators, from duteomechanial dwices such as layboards or from other computers over digital communication ling. <u>Memory Unit</u>: The function of the memory unit is to store pologiams and data. Thue are two classs of storage called primary and Sciendery. Primary storage is a fast memory that operates at electronic speeds. Secondory storage is used when large amounts of clate and many programs have to be stored., patralearly for information that is acceded in flequently.

Asithemetic and Logical unit : - most of the computer operations are executed in the All of the processor. Suppose two numbers located in the memory ale to be added. They are brought into the processor, and the actual addition is carried out by the ALV. The sum may Thenke stond in the memory or retained. in the processor for immediate use. For any other Alv operations the operands ai proyet into the processor, they are stored in high - speed storage elements Called registers. The control and alithmetic and logic Unit's all many times faster than other durices connected to a computer system. This enables a single parounor to control a number of external during. such as Keyboards, displays, magnetic and optical disks. output unit: - This unit is the counter part of input unit. It's function is to Send perouned scrults to The outside world. Example - printer, plotter. Some units, such as graphics displays, Perovide both an output function and an input function.

control Unit: - The operation of other units must be coordinated. in some way. This is the task of the control unit. The control Unit is the name center that sends control signals to other units and serves Their states. The connections among the functional Units are not shown , there connections which can be made in several ways. Information handled by a computer can be Categorized in to instructions or data. Instructions are explicit commands that. Govern The transfer of information within a computer as well as between The computer and its Ilo dwices .. [ Diageam 3 m Explanation 7m.

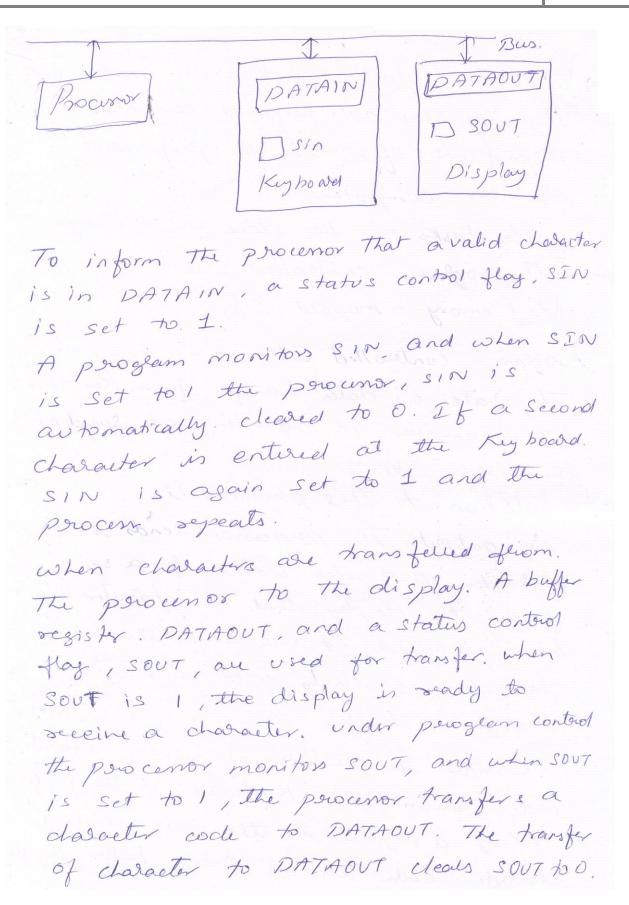

b. What is bus? Explain single bus structure with the help of neat diagram. (8) Answer:

. A group of lines That serves as a connecting path for several dwices. is called a bus. In addition to The lines that carry the dater, the bus must have lines for address and. control purposes. Single bus storeture is the simplest way to interconnect functional units Because the bus can be used for

only one transfer at a time, only two Units can actively use The bus at any given time as shown in the diagram. output Procenor memory Bus control lines are und to albitrate multiple requests for une of the bus. The main vistue of The single bus structure is its low cost and its floxibility for altaching peripheal durias. The durius connected to a bus vary widely in Their speed of operation. An efficient transfer melhanism that is not constrained by the slow dwices and. That can be used to smooth out The information transfer timinings among. perocernors, memories, and external durices. is to use a buffer registers with the durices to hold. The information during trans fers. Digram - 2m Explanation - 4M.

Q.3 a. Explain how data transfer is achieved between memory of a computer and the outside world. (10) Answer:

3 (a). Input/Output operations de essential, and. The way they are performed can have a. significant effect on the performance. of the computer. Ilo tasks can be done in two ways. (1) Program - controlled Ilo. (2) Memory - mapped Ilo. Program - contend Iled Ilo. The rate of data transfer from Keyboard to a computer is dependent on speed of the user. typing. Solution to this publicm. is. on output, The processor sends the first chalacter and Then waits for a signal. from the display that the chosarter has been scenived. It then sends the second character. Similarly input is received. Thorough a buffer. Consider the peroblem of moving a character code ferom the Keybaard to the profemor Striking a Key Stores the corresponding Character code in an 8-bit buffer. segister of the Reyboard. called DATAIN.

memory-mapped 26 many computers use this allangement in which some memory address values are used to sefer to peripheral device buffer registers, such as DATAIN and DATAOVT. No special instructions are needed. to aller the contents of These registers, data can be transferred between These registers and The plucemor using. move, store, & Load instructions Example: contents of The Keyboard character buffer DATAIN can be transfuel to register RI in the processor by The instruction Move Byte DATAIN, RI contents of register RI can be transferred to DATAOUT by The instructions. MoveByte RI, DATAOUT. The status flags sin and sout are au to matically cleared when The suffer registers DATAIN and DATAOUT ale referenced. diguam 2 m Explanation 8 m.

b. Define subroutine. Explain linking of subroutines using link register. (6) Answer:

A particular subtask need to be. performed many times on different. dater values. Such subtask is usually called a subsoutine. when a program branches to a subrouting we say that it is calling the subroutine. After a subsoutine has been executed, the calling program must service execution continuing immediately after. The instruction That called the Subroutine. The subroutine is said to return to the program Itat called it by executing a scholing instruction. Since the subsoutine may be called ferom different places in a calling peroglam, provision must be made for schurning to appropriate location. The location where The culling program sesures execution is the location pointed to by The updated PC while the call instruction is being executed. Here the contents of the PC must be saved by the call instruction to enable correct roturn to the calling program. Subsoutine linkage method. The simplest subsource linkage method is to Same the setion address in a specific location. i.e a register called linkage or link register when the subsoutire completes its tark. the Retion instruction setans to the calling

the relian instruction indiscetty. Itorough the program by branching indiscetty. Itorough the link register.

The call instruction is just a special branch instruction that performs the following operations. \* store the contents. of the PC in the link register. \* Branch to The target address specified by the instruction. The seturn instruction is a special instruction that performs the operation: \* Branch to the address contained in the link register. memory Subsoutine Calling memory location. SUB. location Porostam Birst instruction. Call SUB \_\_\_\_ 1000 200 nept instruction < 204 Return 1000. PC 204 Linc 204. Call. Return. Example 2M Explanation 4m.

(8)

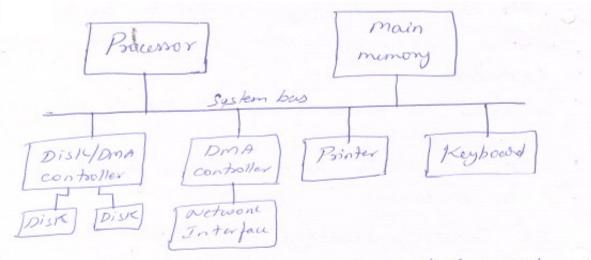

## Q.4 a. Explain the use of DMA controllers in a computer system.

Answer:

A DMA controller connects a high-speed network to the computer bus. The disk controller network to the computer bus. The disk controller which controls & disks, also has DMA capability indich controls two DMA channels. It can perform and provides two DMA channels. It can perform two independent DMA operations, as if each two independent DMA controller. The registers disk. had its own DMA controller. The registers hered to store the memory address, the word court, hered to store the memory address, the word court, and are duplicated, so that one can be used with each

cluirce. To start a DMA transfer of a block of data gerom the main memory to one of the dists a perogean writes the address and word court information into the segisters of the corresponding information into the segisters of the corresponding channel of the disk contenditor. It also channel of the disk contenditor. It also further schieval. when the DMA transfer is further schieval. when the DMA transfer is completed done bit is set. and it IE bit is set the controller sends an intellight signed to the proamor and set the IRQ bit.

Status Bit is used to second information regalding whether the transfer took place. Comethy or errors occurred. TExplanation 6m Figure 2m.

#### b. Define Bus Arbitration. Explain centralised Arbitration.

(2+6)

Answer:

BBSY BR Processor DMA DMA Controller J B62 2. The bus arbiter may be the procentor or a separate unit connected to The bus. Abone diaglam processor contains the bus arbitration circuitoy. Procenor is the bus master unless it grants bus master ship. to one of the DMA controllers. A DMA controller indicates that it needs to become the bus master by activating the Bus - Request line, BR. The signal on The Bus - Request line is the logical OR of the bus requests from all the durices connected to it. when bus - request is actuated, The procenor activates the Bus-Grant signal, 262, indicates to the DMA controller that it can become the bus master. or use the bus. when it becomes free. This signal is connected

**JUN 2015**

to all DMA controllers Using a daisy-chain fashion. Thus, if DMA controller 1 is requesting the bus, it blocks the propagation of the grant Signal to other durices. The aulent bus master indicates to all, durtes that it is aring the bus by activating another open-collector line called Bus-Busy BBSY. After receiving the Bus-Grant signal, a DMA controller waits for Bus-Bury to prevent other devices. from using the bus at the same time Following sequence of events for the durian. when DMAQ. requests and acquires, bus mastership and later scleases. the bus, is depicted below. -> Time. BR BGI B62 BBSY Drit Controller Bus Epsocenor Figure & wave forms 4 m Explanation 4 m

(8)

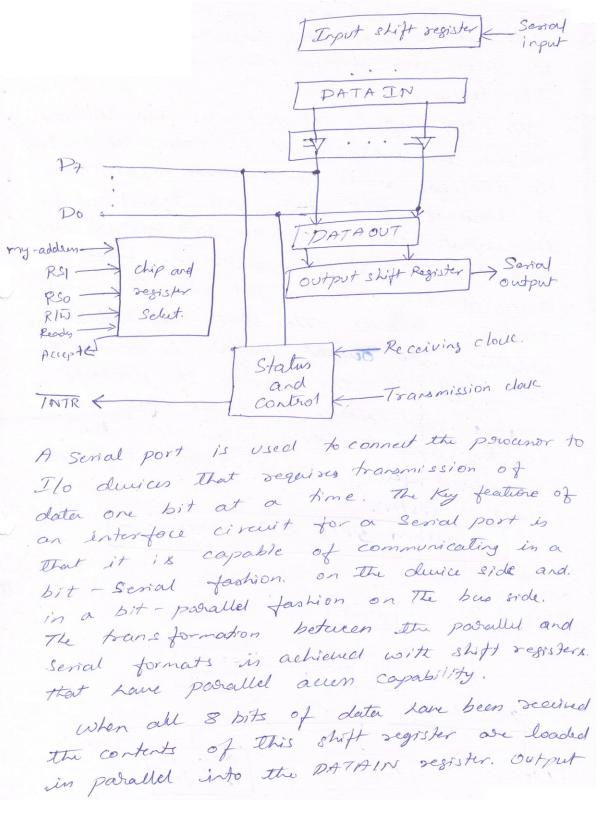

## Q.5 a. Explain serial port with the help of serial interface block diagram.

Answer:

dater in The DATAOUT register all loaded into itte output shift register, forom which the bits are shifted out and sent to the Ilo device. The SIN flag is set to I when new data are loaded in DATAIN. It is cleated to 0 when the processor reads the contents of DATAIN. As soon as the date are transfilled from the input shift register into the DATAIN. register; The shift register can shift start. accepting the next 8-bit character from the Ito device. The SOUT flag indicates whether the output buffer is available. It is cleased to a when the procenar writes new data into the DATAOUT. register and set to 1 when data are transferred. Jerom DATAOUT into the output Shift register. Tipiaglam 3 M Explanation. 5 m.

b. Explain the use of PCI bus in a computer system. Answer:

Host main PCI bridge PCI bus. Etternet interface Printer Diskl

(8)

· PCE is a low cost bus that is truly prounor indypendent. An important peation that the PCI pioneend is a plug-and-play Capability for connecting Ilo durices. The per is designed to support a write operation the procenor sends a memory address followed by a sequence of data words, to be written in sucurine memory locations starting at that address. The bus supports Three address space. memory, Ilo, & configuration. The reprintinge provides a separate physical connection for the main memory. At any given time, one dwice is the bus master. It has the right to initiate data transfers by every read and write, commands. A master is called at initrator in PET terminology. The addressed durice that responds to read and write commands is called a talget. The main bus signals used for transfelling dater are. CLIK A33-MHZ OF 66 MHZ clove FRAME# Sent by the initiator to indicate the duration of a transaction.

## **JUN 2015**

32 addres/dater. lines, which may be AD optionally increased to 64. CIBE# 4 command / byte - enable lines (3 for 64 - bit bus) IRDY#, TRDY# Initrator - ready and Target\_ ready signals. A response from the device DEVSEL# indicating that it has seengaized its address and it's ready for a data transfer transaction. Initialization Device select. ID SEL# Signals whose name ends with symbol # are asserted when in The low voltage state. A complete transfer operation on the bus, involving an address and a burst of data is called a transaction. Individual word transfers within a transaction are called phases. Diaglam 2M Explanation 6M.

#### Q.6a. Describe the working of static RAM cell.

#### Answer:

6 (a). memories that consists of circuits capable of retaining Their state as long as power is applied. are Known as state memories. The following figure shows static RAM cell. Ь b 12 Ti Word lines -Bit lines Two inverters are cross - connected to form a latch. The latch is connected to two bit lines by transistors T. E. T. These transistors act as switches that can be opened or closed under control of the word line. when the word line is at ground level, the transistors are turned off and the latch retains its state. Read operation In order to read the state of the SRAM cull the word line is activated to close switches To and T2. If the cell is in state 1 the. Signal on bit line b is high and the signal on bit line b' is low.

(4)

**JUN 2015**

Sense/Write circuits at the end of the bit lines monitor the state of band b' and set the out put accordingly. Worte Operation The state of the cell is set by placing The appropriate value on bit line b and its complement on b' and then advecting the word live. This forces the cell into the corresponding state. The sequined signals on the bit lines are generated by The Sense/Write Circuit. Diaglam 2M Explanation 2M

#### b. Write the timing diagram for burst read of length 4.

(6)

Answer:

Clock \_\_\_\_ RIW 775 RAS TTA CAS TIL COL Address 77 Row Data D'aylan of waveforms 6m

c.Explain different types of read only memories.

(6)

#### Answer:

6(C) The different types of RAMS at (1) ROM (2) PROM (3) EPROM. (4) EEPROM. ROM cell. Bitline. word line. > E rist connected to store a ]. A logic value o is stored. in the cell if the transistor is connected. to ground at point P. other wise all is stored. The bit line. is connected. Through a sensitor to the power supply. To read the state of the cell. The word line is activated. Thus, the transistor switch is dosed. and the voltage on The bit line drops to rear zono if the is a connection between the transistor and. ground. It there is no connection to ground The bit line semains at The high voltege, indicating a 1. A sense circuit at the end of The bit line generates the Proper output Value. Data are written into a Rom when it is manufactured.

**JUN 2015**

PROM. -> Programmable ROM. (PROM). Programmability is achieved by inserting a fuse at point P. Befox it is programmed, the memory" contains all o's. The user can insect Is at the sequined locations. By bulning out the funs at these locations using high-addent pulses. This phous is irrenorble. EPROE ->. Erasable Programmable Rom. Reperogrammable Rom it has structure similar to the Rom cell, the connection. to ground. is always made at point & and a special transistor is used, which has the ability to function either as a normal transistor or as a disabled. transistor That is always turned off. EEPROM - Electrically Erasable Programmable Rom In this type of Rom's it is possible to clase the cell contents selectively. The only disadvantage of EEPROM. is that different voltages are recelled for chaning, writing, & reading the stored data. Diaylam 2M. Explanation 4M.

Answer:

### Q.7 a. Explain virtual-memory address translation without using TLB.

(8)

7.(a). Viotual address feiom processor Page table base register Vistual page number Page table address offer PAGE TABLE Page flame control Page frame in memory bits Physical address in main Each virtual address generated by the procentor whither it is for an instruction fitch or an operand fetch/store operation, is interpreted. as virtual page number Chigh Order bits). followed by an offset (low-order bits) that specifies the location of a particular byte (or wood) within a page. Information about the main memory location of each page is Kypt in a page table. This information includes the main memory address where the page is stored, and The cullent states of the page. An alea in The main memory that can hold ore page is called a page frame. The statting address of the page table is Kept in a page table base register. By adding the vistual page no

**JUN 2015**

to the contents of This register, the address of The corresponding entry in the page table is abtained. The contents of this location give. The istarting address of the page if That page currently resides in The main memory. Each entry in the page table also includes Some control bits that describe the status of The page while it is in The main memory. One pit indicates validity of The page. Another bit inducates whether the page has been modified dwing its, residency in The memory. As in cache memories this information is needed to determine whether the page should be written back to the disk before it is senored from the main memory: to make soom for another page Diagram 3 m. Explanation 5 m.

b. Explain 4-bit adder with carry look ahead logic. Answer:

(8)

Carry bookahead logic.

A fast adder circuit must speed up the generation of The cally signals. The logic expressions for S; (sum) and G;+, (cally-out) of staye i all.  $S_i = \chi_i \oplus Y_i \oplus C_i$ K  $C_{i+1} = \chi_i y_i + \chi_i c_i + y_i c_i$ Factoring The second equation into  $C_{i+1} = \chi_i y_i + (\chi_i + y_i) C_i$ We can write. Ci+1= Gi+PiCi where.  $G_i = \chi_i y_i$  and  $P_i = \chi_i + y_i$ The expressions G; & P; are called. the generate and propagate functions for Stage 1. The carriers for a 4 bit adder can be implemented. as. C1 = Go + Polo  $C_2 = G_1 + P_1 G_0 + P_1 P_0 C_0.$  $C_3 = G_2 + P_2 G_1 + P_2 G_1 G_0 + P_2 P_1 P_0 C_0.$  $C_4 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0$ TBP2P, PoG.

The carriers are implemented in the block. labeled carry-look ahead logic. An adder implemented in This form is called a carry look ahead adder. Delay Through the adder is 3 gate delays for all carry bits and 4 gate delays, for all sun bits. Diagram 3M. Explanation & equations 5M.

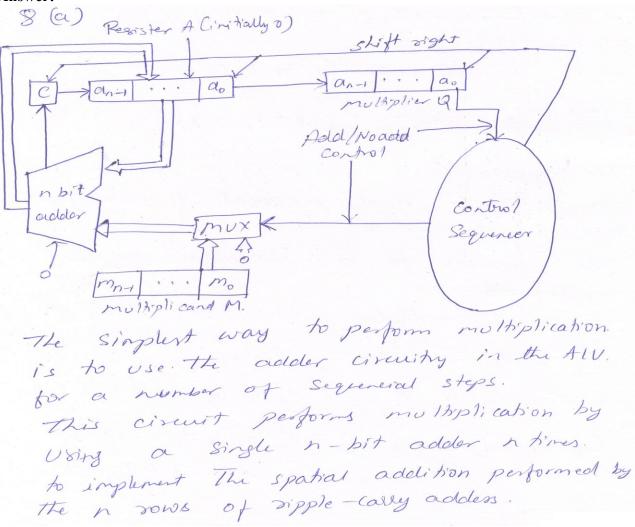

## Q.8 a. Explain sequential circuit binary multiplier with an example.

Answer:

(8)

**JUN 2015**

Register A and & combined hold PP; astile maitspler sit 2; generates The Signal. Add/woodd. This signal controls The addition of the multiplicand, M. to PP; to generate PP(i+1). The product is computed in n cycles. The partial product grows in length by one bit per cycle. forom. The instal vector, PPO, of nos in register A. The cally out from the adder is stored in Hip-Hop C. multiplier is loaded to Register Q. multiplicand is loaded to Register M. Cand A ale challed to O. At the end of each cycle. C. A. & Q ale Shifted right one bit position to allow for growth of the pathral product. as The multiplier is shifted out of register 9. Beeaun of this shifting, multiplier bit 9; appeals at the LSB. position. of 9. to generate the Add/woodd signal at the correct time. starting with go during the first cycle, 9, during the second cycle, and soon. After they are used, the multiplier bits are discarded by the right-shift operation.

| Example M [110]                                        |                    | Z Inthat                           |

|--------------------------------------------------------|--------------------|------------------------------------|

| $\begin{bmatrix} 0 & 0 & 0 & 0 \\ C & A \end{bmatrix}$ | <u>[1011</u><br>Q. | Configuration.                     |

| 0 110)<br>0 0 110                                      | 101)               | L. Add J. Fisht<br>shift. J cycle  |

| 1 0011<br>0 1001                                       | 1101               | Shift J second<br>shift J cycle.   |

| 0 1001<br>0 0100                                       |                    | Swo add J. Third<br>shift J. cycle |

| 1 0001                                                 |                    | Add J Foulth<br>Shift J cycle.     |

| Product                                                |                    |                                    |

| Diaglam 3M. Explanation 4M.                            |                    |                                    |

| Example 3m                                             |                    |                                    |

(4)

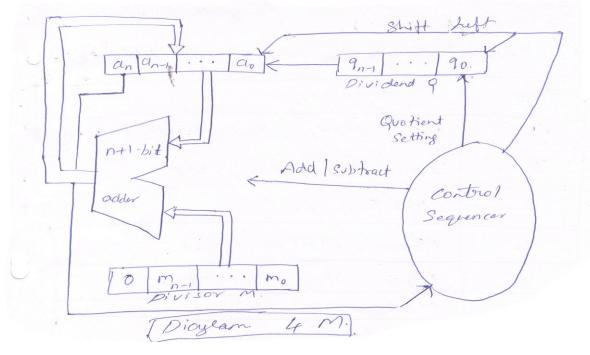

## b. Write the circuit arrangement for restoring division.

#### Answer:

#### c. Write the algorithm for non restoring division.

(4)

#### Answer:

Algorithm for non-sistoring division. Step1: Do the following n times. 1. If the sign of A is O, shift A and Q left one bit position and subtract. M left one bit position and subtract. M from A: otherwise, shift A and Q left and add m to A. 2. Now, if the sign of A is 0, set go to 1; otherwise, set go to 0. Step 2: If the sign of A is I, add mtot. TAlgorithm 2m

Q.9

a. Write the control sequence for the following:

(5×2)

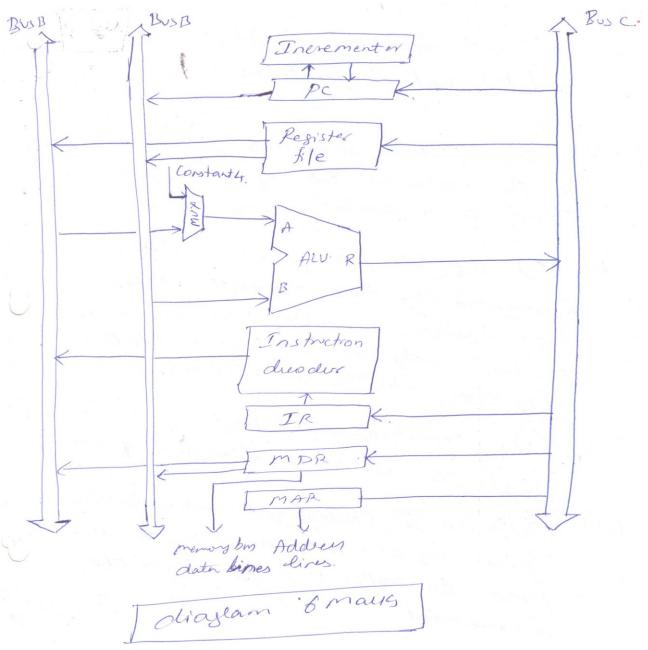

## b. Write the three bus organization of the data path.

#### Answer:

## **TEXT BOOK**

1. Computer Organization, Carl Hamacher, Zvonko Vranesic, Safwat Zaky, 5th Edition, TMH, 2002

(6)