(4)

# Q.2 a. Write a note IC's classification. Answer:

b. Reason out why integrators are preferred over differentiators in analog computers. (2)

Answer:

The differentiates circuit heffers from the limitations on it's stability and noise proble us, at high frequencies. Hence differentiatss are not preferred en analog compretess. 07

c. With the help of a functional block diagram, explain the working of an OPAMP. (6)

Answer:

Functional block diagram of an opamp

1

d. An amplifier has a differential gain of 400 and CMRR of 50 dB. If  $V_{in1} = 50 mV$ ,  $V_{in2} = 60 mV$  and  $V_{noise} = 5 mV$ , determine the differential output and common mode output. (4)

Answer:

$$V_{0} = (V_{ig} - V_{i_{1}}) Ad = (60 - 50) \times 400 \text{ mv}$$

$$= 4000 \text{ mv}$$

$$\int = 20. \log_{10} \frac{Ad}{A_{c}}$$

$$2 \cdot 5 = \log \frac{400}{A_{c}} \Rightarrow A_{c} = 10264 \quad 02$$

$$Common Mode Output | Noise 0| p$$

$$= (V_{i noise}) \times A_{c} = 5 \text{ mv} \times 1.264$$

$$= 6.32 \text{ mv} \qquad 02$$

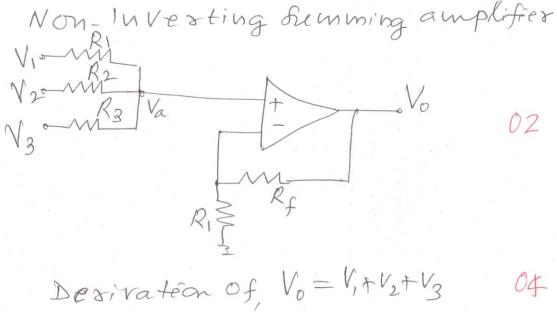

Q.3 a. Realize a non-inverting summer using OPAMP. Answer:

(6)

## c. What are the requirements of a good instrumentation amplifier?

(4)

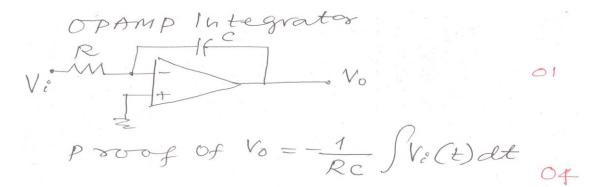

## Q.4 a. With relevant equations show how OPAMP could be used as an integrator. (5)

Answer:

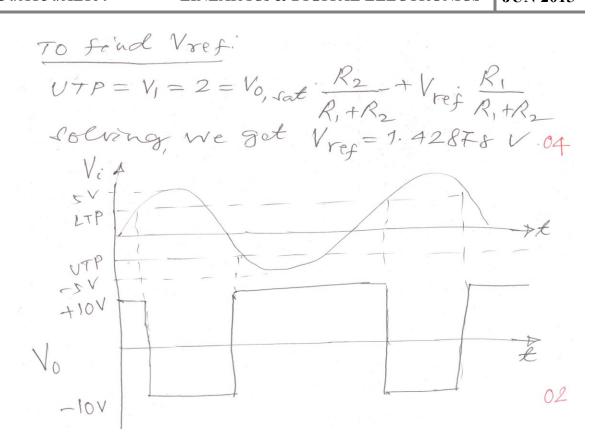

b. Design an OPAMP Schmitt trigger for the following specifications. UTP = 2V, LTP = -4V and output voltage swings between  $\pm 10V$ . If the input is  $V_i = 5 \sin \omega t$ , plot the waveforms of the input and output. (7)

OPAMP Schmitt Trigger

N:

$$K_{1}$$

$K_{2}$

$V_{1}$

$V_{2}$

$V_{1}$

$V_{2}$

$V_{1}$

$V_{2}$

$V_{1}$

$V_{2}$

$V_{1}$

$V_{2} = V_{1} = + V_{0}$ , sat  $\frac{R_{2}}{R_{1} + R_{2}} + V_{1} \cdot \frac{R_{1}}{R_{1} + R_{2}}$

$L TP = V_{2} = - V_{0}$ , sat  $\frac{R_{2}}{R_{1} + R_{2}} + V_{1} \cdot \frac{R_{1}}{R_{1} + R_{2}}$

$Hyptersis, V_{H} = V_{1} - V_{2} = 2 - (-4)$

$= GV$

$G = 2 V_{0sat} \cdot \frac{R_{2}}{R_{1} + R_{2}} \Rightarrow \frac{R_{2}}{R_{1} + R_{2}} = \frac{G}{10}$

$ar 3R_{1} + 3R_{2} = 10R_{2} \Rightarrow 3R_{1} = 7R_{2}$

$Let R_{1} = 1K$ , then  $R_{2} = \frac{3}{T} \times 1K = 0.424Kn$

c. Differentiate between linear and non-linear operation of OPAMP. Give one example for each. (4)

For a certain range of the comput ét acts as a linear device othermse ét is a nonlinear device. Hence, the OPAMP applications are accordingly classified as linear and non linear. Examples for Linear application Adder, Substractor, voltage follower Example for Mon-linear application camparates, peak detects. GA

Q.5 a. Suggest suitable values of resistors and reference voltage for a 4 - bit R - 2R ladder type DAC, if the resolution required is 0.5 (4)

Griven

$$h = 4$$

, Resolution = 0.5V

Resolution of an  $h-bit R-2R$

$DAC = \left(\frac{1}{2h}, \frac{VR}{R}\right)R_{f}$

Where  $V_{R} = Ref. Valtage$ .

Let  $V_{R} = 10V$

Resolution =  $\frac{1}{2h} \times \frac{10}{R}$ .  $R_{f} = 0.5$

$= \frac{1}{16} \times \frac{10}{R}$ .  $R_{f} = 0.5$

$= \frac{1}{K} \times \frac{10}{R}$ .  $R_{f} = 0.5$

$R_{f} = \frac{10}{8} = 1.25$

$R_{f} = 10K$ , then  $R = 12.5$  km of

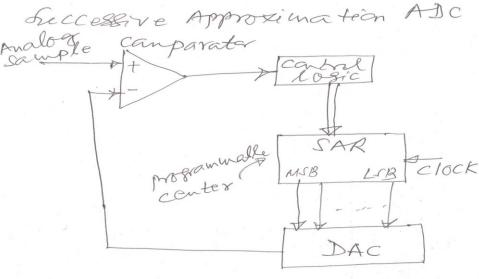

b. With a neat sketch, explain the working of a successive approximation ADC(6) Answer:

Watcin

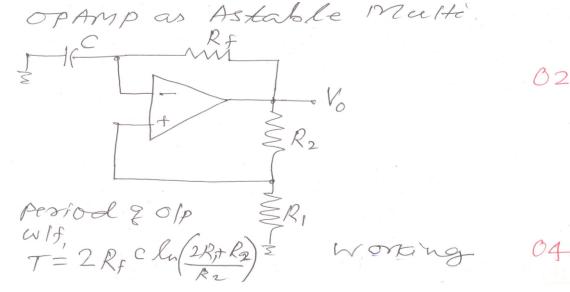

c. Discuss how OPAMP could be used as a free running oscillator. Answer:

Q.6 a. Discuss the advantages and limitations of digital techniques. (8) Answer: Refer pages 6 to 8 of Text Book

b. Explain: (i) BCD code (ii) Alphanumeric codes (8) Answer: Refer pages 33 to 36 of Text Book

02

04

(6)

## Q.7 a. Perform the following operations:

- (i)  $(5531)_8 (3261)_8 + (100)_{10}$

- (ii) Find 'x' in  $(211)_x = (152)_8$  (4)

Answer:

$$Convert Octal to decimal

(5531)_8 = (2905)_{10}

(3261)_8 = (1713)_{10}

(5531)_8 - (3261)_8 + (100)_{10} =

= (2905)_1 - (1713)_1 + (100) = (1292)_{10} 02$$

(i)

(211)\_x = (152)\_8

2n^2 + x + 1 = 1x8^2 + 5x8 + 2x8^0

= 106

Aoling  $x = 7$

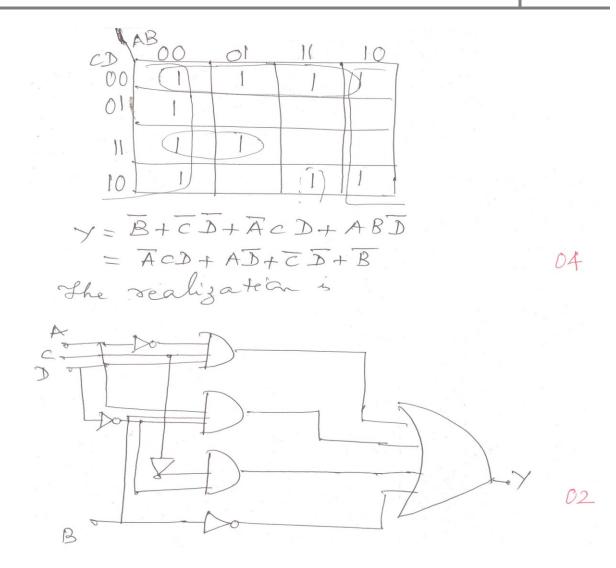

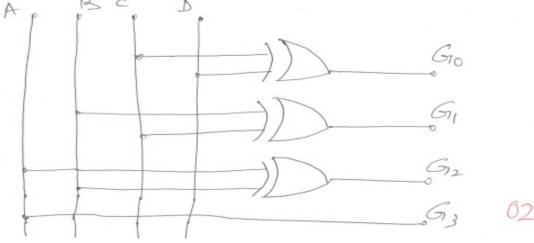

b. Minimize the following logic function using K-map and implement it using logic gates

$$Y(A, B, C, D) = \sum m(0, 1, 2, 3, 4, 7, 8, 9, 10, 11, 12, 14)$$

(6)

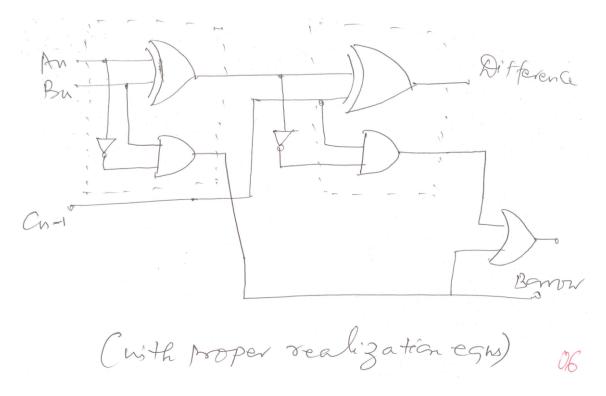

#### c. Realize a full subtractor using two half subtractors.

(6)

Frell Substractor from half Lubstractors The general equations are Dhy=An DBn, Cny=An.Bn Paifference, Camp. The circuit is as below

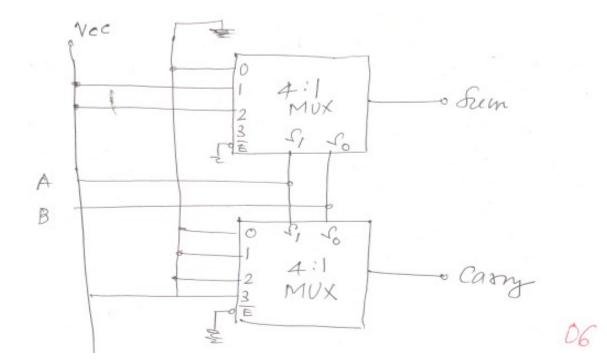

#### Q.8 a. Implement a half adder using multiplexers.

(6)

**Answer:**

such table for a half adder in Camp hem = Im (1,2)  $Carry = \Sigma m(3)$ about is shown next page Using two 4:1 MUX

b. Design an edge-triggered J-K flip-flop using NAND, OR gates. Explain its operation for positive edge triggering. (10)

Answer:

Dosign of Binary to Gizay Converter Truth table 02 Simplification of Boolean equations. 06 Logic diagram

(4)

#### Q.9 a. What is race around condition and how it is eliminated?

Answer:

Race around condition explaination 02 Remedy: Master slave Flep flop 02

b. Compare synchronous and asynchronous counters. Find the maximum frequency of a clock pulse at which the 4-bit ripple counter operates reliably. Assume delay of the flip-flops as 40 ns and the pulse width of strobe signal is 25 ns. (6)

Answer:

In sipple Casmchronous caenters), output Of one flip flop is connected to the clock input of the next stage. But Hence the delay accume lates. Hence Speed is Less The Synchronous counters, clock is applied to all the flep flops of the cauter simultaneously and hence cheveases the speed of operation. Synchronous cauters are faster 03 Poshlem. N=4, td= 40 MB, Ts= 25 hs  $f \leq \frac{1}{N(td) + T_s}$  $\leq \frac{1}{4(40 \times 10^9) + 25 \times 10^9}$ < 5.4 MHZ i. fmax = 5.4 MHZ. 03

12

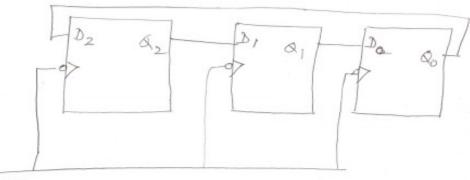

- c. Discuss how shift registers could be used for the following applications:

- (i) SIPO

- (ii) Ring Counter

- (iii) Sequence generator

(6)

Answer:

S/P converter The SIPO shift register is used to convert sesial data in parallel form. consider the size of the word is 8 bits. The 8-bit sipo shift register receives. the data bit by bit with clock pulse. At the end of 8th clock pulse, the 8-bit data is available ares the eight out That lines of the shift Jegister. 02

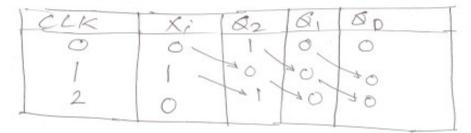

@ Ring Counter.

CLK

It is a SISO Shift register confi -suration. output Q's of the last flip flop is connected to the ilp of the first flip flop.

02

Sequence Grene rat ill zed Logic binational generates sequence go a Logic Cht gen 4 Sec  $\mathcal{O}$ in cation Qo Q1 comme -1 QN-2  $\times i$ 02 regista

### **TEXT BOOKS**

- I. Linear Integrated Circuits, Revised Second Edition, D Roy Choudhury, Shail B. Jain, New Age International Publishers

- II. Digital Systems Principles and Applications, Ninth Edition, Ronald J Tocci, Neal S Widmer and Gregory L. Moss, Pearson Education, 2008