AE74 VLSI DESIGN JUNE 2014

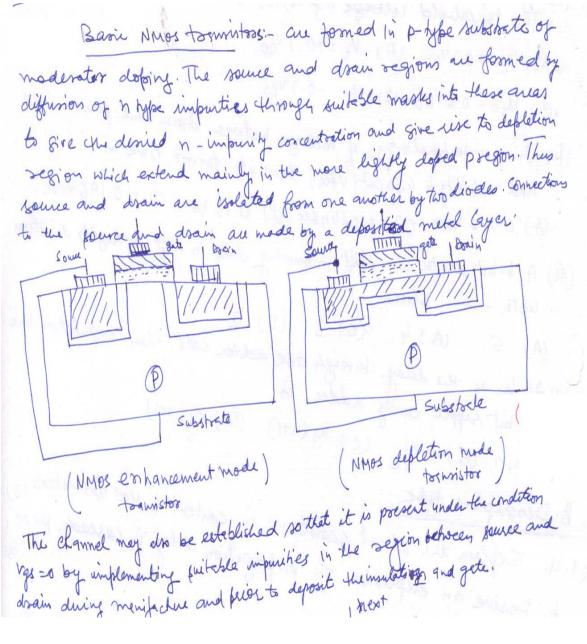

# Q2 (a) Explain basic n MOS transistors.

#### Answer

Q2 (b) Explain the thermal aspects of processing nMOS and CMOS devices.

Answer: Page Number 17 & 18 from text book

Q3 (a) Derive the relationship between transconductance and output conductance for MOS transistors.

Togos conductorce expresses the relationship between of purcent & Fds and I/p Wallage vgs and is diffined as gm = & Ids | Vds = Constant Tornit time  $T = Q_C$ Thus Change in current & Fas = & Qc Tas Tas = L<sup>2</sup> HVds & Ids = & QcVds 4 EQC = Cg& Vgs to that & Fas = Cg & Vgg 11 Vas Moss gm = & Jas = Cg h Vas

Evgs L2

In saturation Vas = Vgs - VE gm = Cg4 (Vgs - Ve) Susditte proj= Em & WL gm = με jis 60 W (Vgs-Vt)

or βm = β (Vgs-Vt) Where β= μ tins 60 W

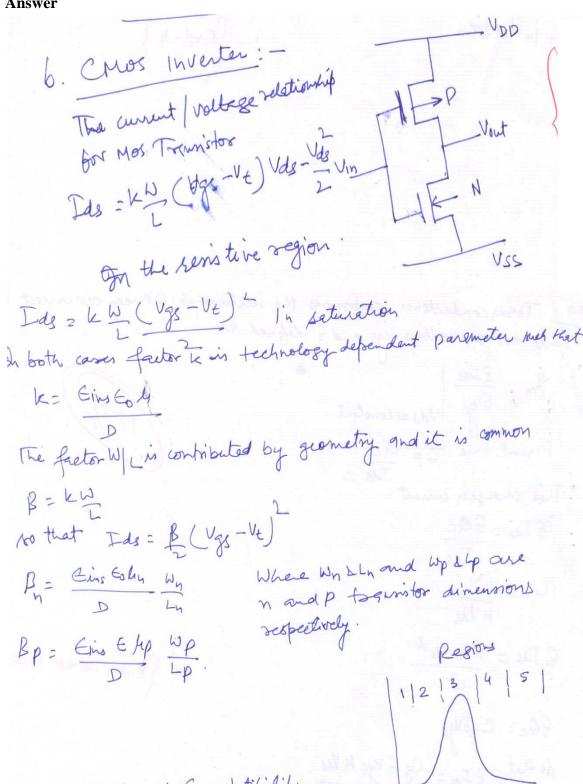

# Q3 (b) Explain CMOS inverter.

Q3 (c) Explain Bi CMOS Latch up susceptibility.

Bierros Latch up Susceptibility. the beniefit of the Bicmos process in that it produces circuits which are less likely to suffer from Latch up problem. This is due to several factors A reduction of substrate resistance - A reduction of Rg + Rw means that a larger lateral coment is necessary to invite latch up and a higher value of holding current is also required. - The pararitic prop tomoistence which is part of the nwell tatch up circuit has its bette reduced owing to the presence of the buried nt layer. This has the effect of reducing carrier lifetime in the on base region and this contributes the seluction in bett.

# Q4 (a) Explain contact cuts in NMOS circuits.

#### Answer

a Contact cuts in NMOS: - When contacts between polysilion and diffusion in Mos are made, there are three possible approaches 1. Poly. to metal then metal to diff 2. a Burnied Contact poly. to diff. When making connections between metal and either of other two layers the process is quite simple. The 2xx2x contect cut indicates an area in which the oxide is to be removed down to the model undulying polysition or diffusion nufsee. When deposition of the motel layer takes place the metal in deposited through the contest out areas onto the underlying area so that contact is made between the layers. Fig. 3.8 and 39. : See Page 69: Banic VLSI dengin Douglas A. Pucknelle?

AE74 VLSI DESIGN JUNE 2014

# Q4 (b) Write down the double metal MOS process rules.

#### Answer

b. Double Netal NOS Process Rules:—

1. Use the second level metal for global distribution of power bourses is Vop and GND (USS) and for clock lines.

2. Use the first level metal for local distribution of power and for signal lines.

2. Double Netal Layers to that the conductors are power and for signal lines.

3. day out the two metal layers to that the conductors are mutually orthogonal wherever possible.

# Q4 (c) Explain design rules for wires in $2 \mu m$ CMOS.

**Answer** Page numbers 77 from text book

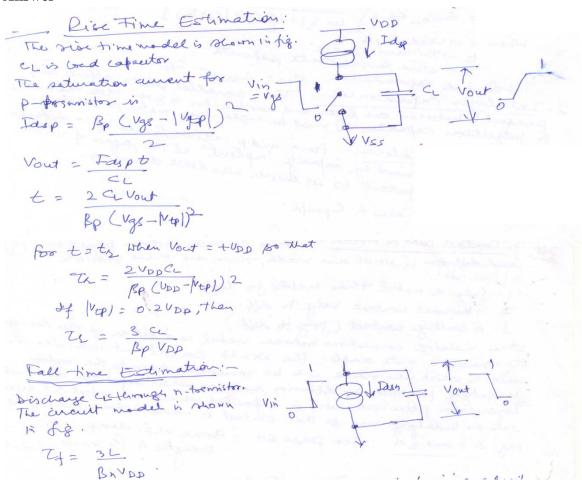

# Q5 (a) Calculate the rise time and fall time of a CMOS inverter.

#### Answer

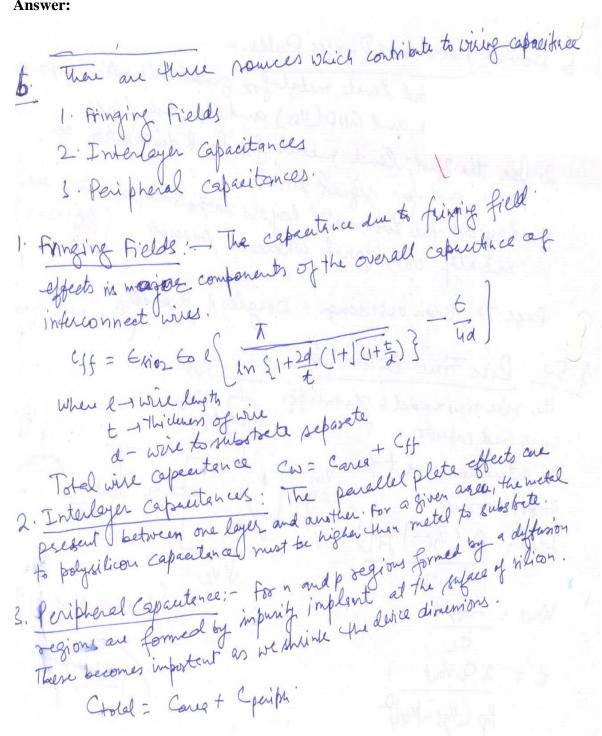

# Q5 (b) Explain the sources of capacitance which contribute to the overall wiring capacitance.

Answer:

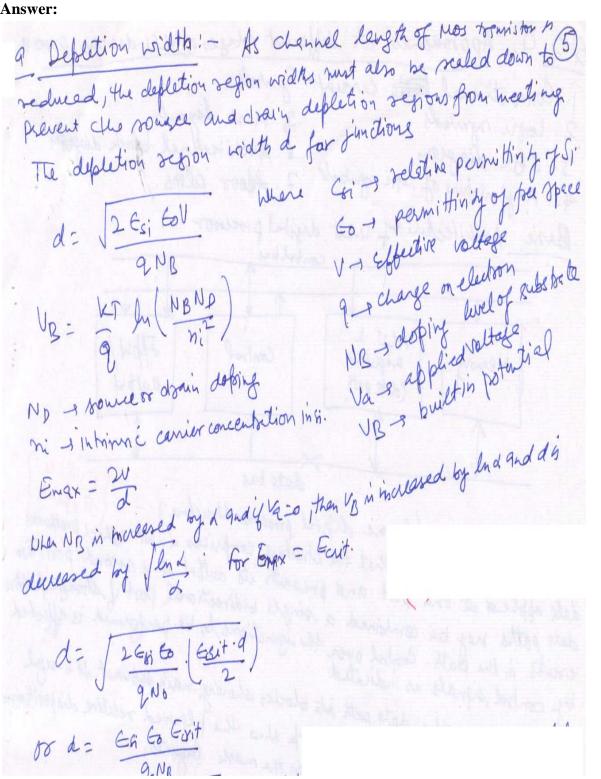

Q6 (a) Derive an expression for depletion width.

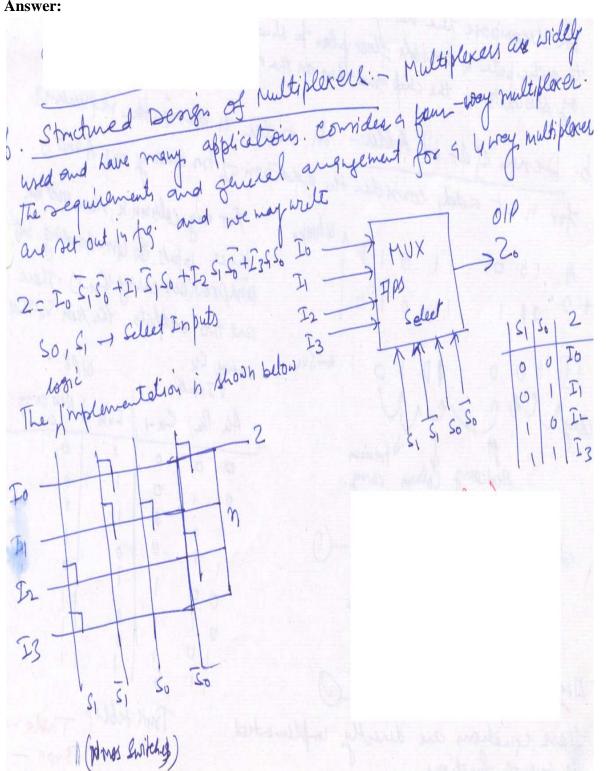

Q6 (b) Explain the structured design of multiplexer.

**JUNE 2014 VLSI DESIGN AE74**

#### Answer:

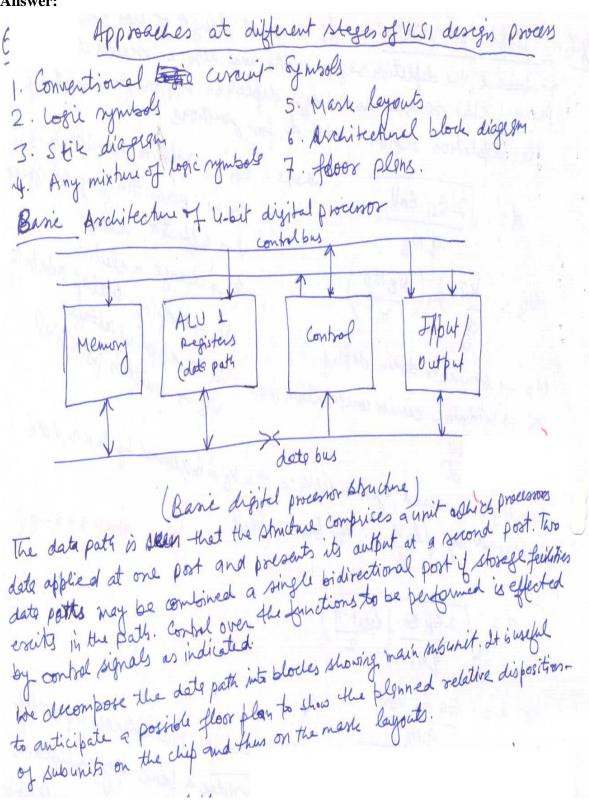

Q7 (a) Where the various approaches used at different stages of VLSI design process? Explain the basic architecture of 4 bit digital processor.

Q7 (b) Design a 4 bit adder.

# Answer: b. Denger of 4-bit Adder: In order to denge the sequents. For n bit add, consider the addition of two binary nos Agner B. 7 three in buts. (Suresponding bits wind previous carry (Ch-1). There are two outputs, the sum Engad carry CK New carry 0 0 0 0 0 Where HR = AhBut ALBU He > Half sym New Carry Cu: Ansm+Hu Cu-1\_0 Tryk teble Shere equations are directly implemented as AND-OR functions.

Q8 (a) What are the factors considered to make a comparative assessment of the dynamic shift registers?

Factors considered to pralee comparative assement for the 6 dynsmic slift register. 1. Area requirement 2. Estimated dissipation 1. Area: consider the case of NMOS designs with buried contects Allow for sharing of von and GND rails between adjacent rows of registereds.

The each hit is The each bit stored will sequire 22/X28x = 1200x for x = 2.5 um, Area partit = 7500 um For CMOS (38XX 28X) x2 = 2100 /2. 7= 9:5 An Area per bit = 13 000 MM 2. Discipation: In come of creas static discipation is very small, The dynamic power consulption PL = m CLUPD + Where m - duty cycle CL + effective bood capacitance f - block frequency. dinmos, 200 = 4Ps Canent = VDD = The static dissipation = VDD X Coment Pp. 72pa Bit stored and 2 pd = 4 B 3. Valatility: - Date in stored by the charge on the gate capacition of each inverter stage so that date storege time is dimited to I wise cor less.

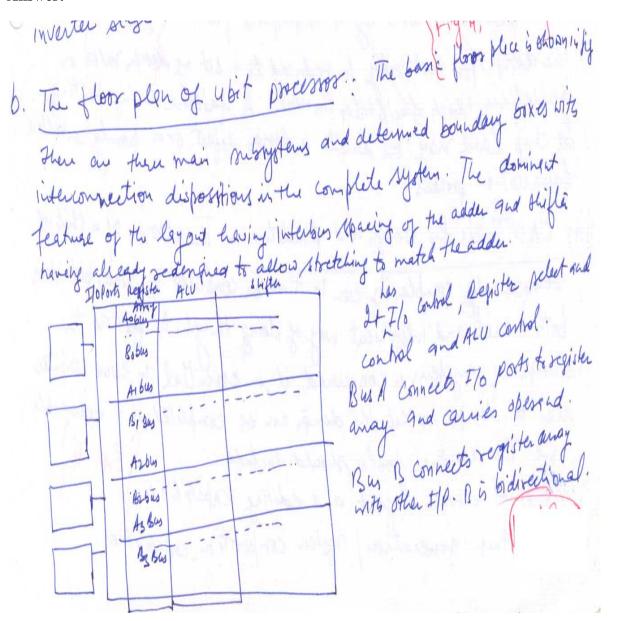

# Q8 (b) Explain floor plan layout of a 4- bit processor.

#### **Answer:**

# Q9 Write short note on:

- (i) Design Rule Checkers

- (ii) CIF code

- (iii) CAD Tools for design and simulation

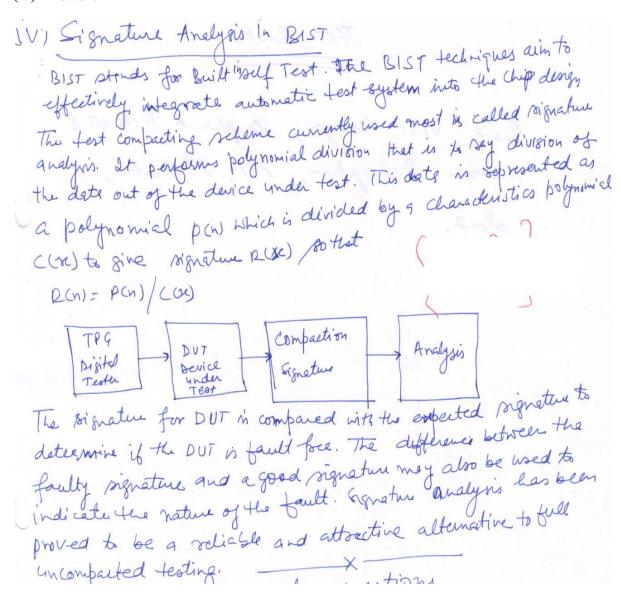

- (iv) Signature Analysis in BIST

(i) Design Roll Checkers: - The cost in time and faility in mark making and fabricating a chip from those marks is such that all possible errors must be climinated before Chetking proceeds. Once a design has been turned into silicon there is little that can be done is check for errors at all styles of 1. At the pencil and paper stage of deoign of leaf-cells. denign, namely. 2. At the leaf-cell level once the layout is complete 3. At subsystem level to check that butting together and wining. up the leaf-cells is correctly done 4 Once the entire system begand has been completed. The nature of Physical layout verification design rule checking stoftware defend on whether the doings onles are absolute or & based ox on whether or not the layout is on a fixed or victual grid.

# (ii) Answer: Page numbers 293 from text book

# (iii) Answer:

(11) CAD Tools for Deogn and Simulation: - The deorgy of a Chip of reasonable complexity can in time be completed by hand, but it is both a hard and inefficient way of doing things. As for as the denon of mystems is concerned, it is essential to have computer aids to denigr no that the denigr can be completed in a reasonable time. The denimer tools should include 1. Physical danien layout and editing capabilities. 2. Structure generation | system composition apositions. 3. Physical varification. It includes denon rule chelling, (9) circuit entractors, ratio rule and other static cheeles and a capability to plot out and or display for visual chacking. 4. Behavioural verification. Simulation at various levels will be sequired to check out the design before one embanks on the expense of turning out the design in solicon.

## (iv) Answer:

# **Text Book**

Basic VLSI Design, Douglas A. Pucknell & Kamran Eshraghian, PHI,  $\mathbf{3}^{\mathrm{rd}}$  Edition, 2007