Q.1 a. Describe the domestic and industrial application of embedded system. Answer:

(a) Application IN INDUSTRY:--TTeleCom

-Thele Com -7 Auto mative applications -7 Domestic applications -7 Robatrics -7 Robatrics -7 Revospace applications -7 Medical equipment -7 Defense systems.

Application In Domestic Printers.

Satellike phones Scannors. Televisions Temperatur Controller. TV-set up Boxes.

b. Show the contents of the PSW register of after execution of the following

**DEC 2015**

instruction. MOV A, #0BFH ADD A, #1BH Answer: 1.0 PSU Pau Bu PSU BU BU 6 5 4 3 2 PSU 6) MOVA, #OBFH ADD A, HIBH 10111111 + IB 00011011 DA a, 0, 0, 0, 1005 0-PSW7: CY=O Since there is no cavity beyond the DT bit. PSW6 : AC = 1 Since there is a corry from the D3 to the D4 but. ISUS : Fo = Unused Rence O. PSWY: Register bank selector bit RSI=0 Smile by default, Bonk 0 is selected. RSW3: Register bank seledor bit RSO=0 Since by default, Bank Q is selected PSW2: OV = O NO COUNTY from D6 to D7 PSW1 : No Used Denie O PSWO: P=1 Since there is an oddy plan of Dnedy in accordedor (1/3) The contentents of the PSW 15 0109 0001 PSW = HIH 2 **© IETE**

c. Explain briefly different types of memories used in 8051. Answer: memories used in gost Eifferen ROM SRAM PROM NV-RAM DRAM TEPROM 7 EEPROM 7 Elash memory EPROM Ly Mask Rom ROM (Read only memory, Rom is also called nonvolatile memory that does not less its contents when the power is twined off. PROM ( Irogrammable Rom) and OTP PROM stefers to the bind of Rom that the user can burn information into . In other words, prom is a user-programmable memory. for every bit of the PROM, there exists a fuse. PROM is programmed by blowing the fuses. If the information burned into prom is wrong, that prom must be discarded since its internal fuses are blown permonently for this reason, prom is also referred to as OTP. frogramming Rom, also called burning Rom, nequires special equipment called a Rom burner or Rom programmer. EPROM (erosable Programmable Rom) and UV-EPROM In EPROM, one can program the memory chip and erase it thousands of times. This is especially necessary during development of the prototype of a microprocessor -based peroject. A widely used EPROM is called UN-EPROM, where UN stands for ultravialet. The only problem with UV-EPROM is that exasing its contents Can take up to 20 minutes. All UN-EPROM clips have a window through which the programmer can shine ultravialet (UV) readiation to exase its contents for this reason, EPROM 4 also referred

0.1.0 to as UN - erosable EPROM ON simply UN-EPROM. To program a UV-EPROM chip, the following steps must be taken: O Its contents must be exased. To exase a chip, semove it from its socket on the system board and place it in EPROM esasure equipment to expose it to UV radiation for 15-20 minutes. (2) Program the clip. To programe a UV-EPROM chip, place it in the ROM burner. To burn code or data into EPROM, the ROM burner wes 12.5 valts or higher, depending on the EPROM type. This Vallage is referred to as vep in the Ov-EPROM data shect. (3) Place the chip back into its socket on the system board. EEPROM (dectrically evasable programmable Rom) EEPROM has several advantages over EPROM, such as the fact that its method of exasture is electrical and therefore instant, os opposed to the 20 minute exasure time required for UV-EPROM. In addition, in EEPROM one Can select which byte to be exosed, in contrast to UV-EPROM, in which the entire contents of Rom are erased. However, the main advantage of EEPROM is that one Can program and erose its contents while still in the system board. It does not require an external erosure and programming device. Flash Memory EPROM: The major difference between EEPROM and flash memory is that when flash memory's contents are erased, the entire device is crossel,

the major option of contents are exased, the entire device is exasel, flash memory's contents are exased, the entire device is exasted, in contrast to EEP-Rom, where one can exase a desired section or byte. Although in some flash nemories recently made available the contents are divided into blacks and the exasure can be done black by black, unlike EEPROM, flash memory has no byte exastre option.

Mask Rom.

Mask Rom negers to a bind of rom in which the contents are - programmed by the IC manufacturer. In other words. it is not a user - programmable Rom. The form mask is well in Ic faborication. Since the process is castly, mask Rom is used when the needed valume is high and it is absolutely contain that the contents will not change.

RAM (grandom access menory)

RAM memory is called volatile memory since cutting off the power to the IC results in the lass of data. Smetimes RAM is also referred to as RAWM (read and write memory), in contrast to Rom, which cannot be written to There are three types of RAM: Static RAM, NV-RAM and dynamic RAM. Each is explained separately.

SRAM (Stehr RAM)

storage cell in static RAM memory are made of flip-flop and therefore do not require refreshing in order to beep their data. This is in Contrast to DRAM.

The problem with the use of flip-flop and therefore each cell sugares at least 6 bansistors to build, and the cell holds only 1 bit of data.

NV-RAM (nonvalable RAM)

whereas SRAM is volatile. There is a new type of nonvolatile RAM Called NV- RAM.

(1) It uses extremely power-efficient shart cells built out of cross (2) It uses an internal lithium battery as a backup energy source.

DRAM (Dynamic RAN) The major advantages of DRAM figh density, cheaper last per bit, and lover power consumption por bit. The disadvantage is that it must be represhed periodically because the capacitor cell loses it charge; futhermore, while DRAM is being

d. Explain Scheduling Algorithms of RTOS. **© IETE**

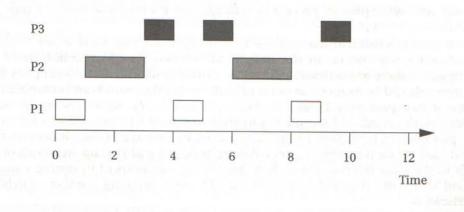

Answer: Scheduling Algabathins of RTOS Shortest Job First Scheduling: The process that requests less CPU burst is allocated the CPU first Process 2 - Case where SIJF request in failure Ples Process 1 Earliest Deadline First Scheduling ! The process that have earlier deadline is having higher priority. Priority is determined by deadline - Case where EDF redults in failure. Process 2 Round Robin Scheduling [ Process 1 - Each process is assigned time interval = If process is still dunning at end of quantum CPU is preempted and given to another process - Issue - length of quantum . Too shipt will cause too many process switches and lowers the CPU efficiency Too long will cause poor response Current . process Current process Netpropess FF1-B-FD HG F B A GI A D-Priority Scheduling - Each process is assigned priority and runable process with highest privity is allowed to fun Priority Issign algorithms are classified as fixed prevoity, dynamic priority or mixed privity Runhable placesses Queue headers Multidevel Queue Scheduling Ready gueue is partitioned 0-0-0 Priority 4 Evority 3 -0-0-0-0 into separate queues: Foreground and background Priority2 - 1 - Each queue has its swort scheduling algorithm Burity Rate Monotonic Scheduling RMS is optimal fixed predority algorithm The shorter period, the higher gristily. If a task set cannot be scheduled using RM algorithm, it cannot be scheduled using any fixed priority algorithm. The deadline q m processes can be met if processor utilization  $U = \stackrel{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\sim}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\overset{\scriptstyle}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\atopi=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\underset{i=1}{\atopi=1}{\underset{i=1}{\atopi=1}{\underset{i=1}{\atopi=1}{\underset{i=1}{\atopi=1}{\underset{i=1}{\atopi=1}{\underset{i=1}{\atopi=1}{\underset{i=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atopi=1}{\atop$ V= processos utilization m=no-d tasks in system G = condeutation tible Pi= Process

e. What is Pipelining? Explain with an example. Answer:

© IETE

**CT74**

**DEC 2015**

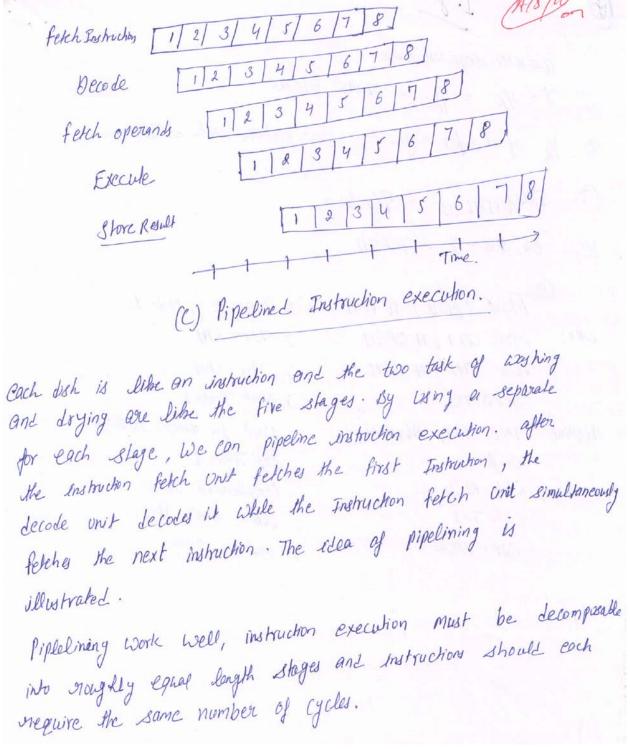

(C) Pipelining Pipelining is a common way to increase the instruction throughput of a microprocessor. We first make a simple analogy of two people approaching the chore of washing and daying eight dishes. In one approach, the first person washes all eight dishes, and then the second person doires all eight dishes. Assuming I minute per dish por porson, this approach sugaines 16 minutes. The approach is clearly inefficent since at any time only one. person is working and the other is idle. Obviously, a better approach is for the second porson is being drying the first dish immediately after it has been Washed. This approach requires only 9 minutes - 1 minute for the first dish to be washed and then 8 more minutes Until the last dish is finally dry. We refer to this latter approach os pipelined. Wash 123415678 2 3 4 5 6 7 8 Ory Time (a) NON pipelines dish cleaning. 1 2 3 4 5 6 7 8 8 3 1/2 (h) Pipelines Juh cleaning.

f. Explain development environment and debugging techniques. Answer:

In this section we take a step back from the platform and consider how it is used during design. We first consider how we can build an effective means for programming and testing an embedded system using hosts. We then see how hosts and other techniques can be used for debugging embedded systems.

## 4.6.1 Development Environments

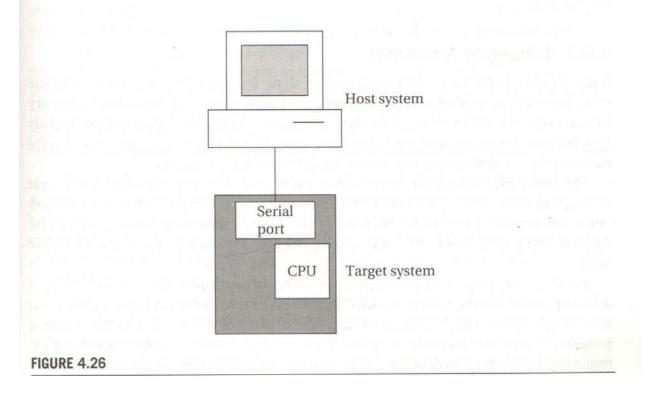

A typical embedded computing system has a relatively small amount of everything, including CPU horsepower, memory, I/O devices, and so forth. As a result, it is common to do at least part of the software development on a PC or workstation known as a *host* as illustrated in Figure 4.26. The hardware on which the code will finally run is known as the *target*. The host and target are frequently connected by a USB link, but a higher-speed link such as Ethernet can also be used.

The target must include a small amount of software to talk to the host system. That software will take up some memory, interrupt vectors, and so on, but it should

generally leave the smallest possible footprint in the target to avoid interfering with the application software. The host should be able to do the following:

- load programs into the target,

- start and stop program execution on the target, and

- examine memory and CPU registers.

A *cross-compiler* is a compiler that runs on one type of machine but generates code for another. After compilation, the executable code is downloaded to the embedded system by a serial link or perhaps burned in a PROM and plugged in. We also often make use of host-target debuggers, in which the basic hooks for debugging are provided by the target and a more sophisticated user interface is created by the host.

A PC or workstation offers a programming environment that is in many ways much friendlier than the typical embedded computing platform. But one problem with this approach emerges when debugging code talks to I/O devices. Since the host almost certainly will not have the same devices configured in the same way, the embedded code cannot be run as is on the host. In many cases, a *testbench program* can be built to help debug the embedded code. The *testbench* generates inputs to simulate the actions of the input devices; it may also take the output values and compare them against expected values, providing valuable early debugging help. The embedded code may need to be slightly modified to work with the testbench, but careful coding (such as using the #ifdef directive in C) can ensure that the changes can be undone easily and without introducing bugs.

## 4.6.2 Debugging Techniques

A good deal of software debugging can be done by compiling and executing the code on a PC or workstation. But at some point it inevitably becomes necessary to run code on the embedded hardware platform. Embedded systems are usually less friendly programming environments than PCs. Nonetheless, the resourceful designer has several options available for debugging the system.

The serial port found on most evaluation boards is one of the most important debugging tools. In fact, it is often a good idea to design a serial port into an embedded system even if it will not be used in the final product; the serial port can be used not only for development debugging but also for diagnosing problems in the field.

Another very important debugging tool is the *breakpoint*. The simplest form of a breakpoint is for the user to specify an address at which the program's execution is to break. When the PC reaches that address, control is returned to the monitor program. From the monitor program, the user can examine and/or modify CPU registers, after which execution can be continued. Implementing breakpoints does

not require using exceptions or external devices. Programming Example 4.1 shows how to use instructions to create breakpoints.

### Programming Example 4.1

#### Breakpoints

A breakpoint is a location in memory at which a program stops executing and returns to the debugging tool or monitor program. Implementing breakpoints is very simple—you simply replace the instruction at the breakpoint location with a subroutine call to the monitor. In the following code, to establish a breakpoint at location 0x40c in some ARM code, we've replaced the branch (B) instruction normally held at that location with a subroutine call (BL) to the breakpoint handling routine:

| 0 | х | 400 | MUL r4,r4,r6 |                   | 0 | Х | 400 | MUL r4,r4,r6 |

|---|---|-----|--------------|-------------------|---|---|-----|--------------|

| 0 | х | 404 | ADD r2,r2,r4 | $\longrightarrow$ | Θ | X | 404 | ADD r2,r2,r4 |

| 0 | х | 408 | ADD r0,r0,#1 |                   | 0 | х | 408 | ADD r0,r0,#1 |

| 0 | х | 40c | B loop       |                   | Θ | х | 40c | BL bkpoint   |

When the breakpoint handler is called, it saves all the registers and can then display the CPU state to the user and take commands.

To continue execution, the original instruction must be replaced in the program. If the breakpoint can be erased, the original instruction can simply be replaced and control returned to that instruction. This will normally require fixing the subroutine return address, which will point to the instruction after the breakpoint. If the breakpoint is to remain, then the original instruction can be replaced and a new temporary breakpoint placed at the next instruction (taking jumps into account, of course). When the temporary breakpoint is reached, the monitor puts back the original breakpoint, removes the temporary one, and resumes execution.

The Unix *dbx* debugger shows the program being debugged in source code form, but that capability is too complex to fit into some embedded systems. Very simple monitors will require you to specify the breakpoint as an absolute address, which requires you to know how the program was linked. A more sophisticated monitor will read the symbol table and allow you to use labels in the assembly code to specify locations.

Never underestimate the importance of LEDs in debugging. As with serial ports, it is often a good idea to design a few to indicate the system state even if they will not normally be seen in use. LEDs can be used to show error conditions, when the code enters certain routines, or to show idle time activity. LEDs can be entertaining as well—a simple flashing LED can provide a great sense of accomplishment when it first starts to work.

When software tools are insufficient to debug the system, hardware aids can be deployed to give a clearer view of what is happening when the system is running. The *microprocessor in-circuit emulator (ICE)* is a specialized hardware tool that can help debug software in a working embedded system. At the heart of an

in-circuit emulator is a special version of the microprocessor that allows its internal registers to be read out when it is stopped. The in-circuit emulator surrounds this specialized microprocessor with additional logic that allows the user to specify breakpoints and examine and modify the CPU state. The CPU provides as much debugging functionality as a debugger within a monitor program, but does not take up any memory. The main drawback to in-circuit emulation is that the machine is specific to a particular microprocessor, even down to the pinout. If you use several microprocessors, maintaining a fleet of in-circuit emulators to match can be very expensive.

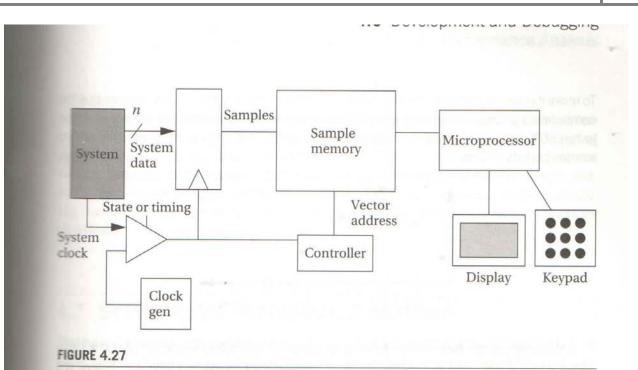

The *logic analyzer* [Ald73] is the other major piece of instrumentation in the embedded system designer's arsenal. Think of a logic analyzer as an array of inexpensive oscilloscopes—the analyzer can sample many different signals simultaneously (tens to hundreds) but can display only 0, 1, or changing values for each. All these logic analysis channels can be connected to the system to record the activity on many signals simultaneously. The logic analyzer records the values on the signals into an internal memory and then displays the results on a display once the memory is full or the run is aborted. The logic analyzer can capture thousands or even millions of samples of data on all of these channels, providing a much larger time window into the operation of the machine than is possible with a conventional oscilloscope.

A typical logic analyzer can acquire data in either of two modes that are typically called *state* and *timing modes*. To understand why two modes are useful and the difference between them, it is important to remember that an oscilloscope trades reduced resolution on the signals for the longer time window. The measurement resolution on each signal is reduced in both voltage and time dimensions. The reduced voltage resolution is accomplished by measuring logic values (0, 1, x) rather than analog voltages. The reduction in timing resolution is accomplished by sampling the signal, rather than capturing a continuous waveform as in an analog oscilloscope.

State and timing mode represent different ways of sampling the values. Timing mode uses an internal clock that is fast enough to take several samples per clock period in a typical system. State mode, on the other hand, uses the system's own clock to control sampling, so it samples each signal only once per clock cycle. As a result, timing mode requires more memory to store a given number of system clock cycles. On the other hand, it provides greater resolution in the signal for detecting glitches. Timing mode is typically used for glitch-oriented debugging, while state mode is used for sequentially oriented problems.

The internal architecture of a logic analyzer is shown in Figure 4.27. The system's data signals are sampled at a latch within the logic analyzer; the latch is controlled by either the system clock or the internal logic analyzer sampling clock, depending on whether the analyzer is being used in state or timing mode. Each sample is copied into a vector memory under the control of a state machine. The latch, timing circuitry, sample memory, and controller must be designed to run at high speed

Architecture of a logic analyzer.

since several samples per system clock cycle may be required in timing mode. After the sampling is complete, an embedded microprocessor takes over to control the display of the data captured in the sample memory.

Logic analyzers typically provide a number of formats for viewing data. One format is a timing diagram format. Many logic analyzers allow not only customized displays, such as giving names to signals, but also more advanced display options. For example, an inverse assembler can be used to turn vector values into microprocessor instructions.

The logic analyzer does not provide access to the internal state of the components, but it does give a very good view of the externally visible signals. That information can be used for both functional and timing debugging.

## 4.6.3 Debugging Challenges

Logical errors in software can be hard to track down, but errors in real-time code can create problems that are even harder to diagnose. Real-time programs are required to finish their work within a certain amount of time; if they run too long, they can create very unexpected behavior. Example 4.2 demonstrates one of the problems that can arise.

g. Generate a frequency of 100 KHz on pin p2.3. Use Timer 1 in mode 1 assume XTAL of 22 MHz. (7×4)

Answer:

| C.                       |                                       |                             |

|--------------------------|---------------------------------------|-----------------------------|

|                          | 100 KH2 Sequare Dave                  |                             |

| $\overline{\mathcal{O}}$ | $T_{z} I/r = \frac{1}{1} = 0/m_{s} =$ | -10.015                     |

| (A)                      | 1/2 of it for high and low            | o portions each = 5.els     |

| Ð.                       | 1/2 of in for o                       | Letterster . I Letter       |

| 3                        | 5.248/0.546 ers = 9 Cycles.           |                             |

|                          |                                       |                             |

| 4                        | 65,536-9 = FFF7H.                     |                             |

|                          | MOV TIMOD, # IOH                      | ; Timer 1, Mode 1           |

| BACK;                    | MOV TLI, # OFTH                       | ; TXI = F7H                 |

|                          | MOV THI, # OFFH                       | ; THI = FFH                 |

|                          | SETB TRI                              | ; Shart Timer 1             |

| AGAL                     | and all all                           | ; wait for timer stallover. |

|                          | CLR TRI                               | : stop Timer 1              |

|                          | CP L P2.3                             | ; Complement P2.3           |

|                          | CLR TFI                               | ; clear timer flag.         |

|                          | SJMP BACK                             | ; neload timer.             |

Q.2 a. What are the criteria for selection of processor for use in an embedded system? (6) Answer:

Sol. 0.2 ul 2 The embedded cystian designer must relect a msa. Up for we in an embedded System. The choice of a processor depends on Ecchnical and near technical aspects From technical perepecture, our unet chorese a processor that can achieve that desired speed within certain pomer, size and cast conderints. Non kalmical aspects may mende prior experties mit a processor and its development 'environment, special licensing arrangment Spred is a particularly difficult processor aspect and so on to measure and compare are could compare processor dark speed, but the muniber of instructions per second. but the clock uple way differ greater among processes the could instead compare instructions per second, but the complexity of each instruction may also differ qually among processors. For example, one processor may require 100 instruction while another presenter may require 300 instruction to preform the same computation power MIPS Bus WICH Peripherals Processor clock. Speed \$100 976 5900 32 2×16K 1GH2 Intel PIEL H1, 256K 12, MMX \$7 10.20 51 8 HK ROM, 128

Intel 8050

12 MMZ

RAM , 32 \$10 Timer, UART

15

one attempt to promote a mean for a faire compa riscon is the sheystone beuchmark. A buchmark is a program intended to be run on different processor to compare their performance. It focuses an exchange a processor's integer alithoustic and string - handling Capabi - lities. Its current version is usilter in C and is in the public domain. Recause most processers can execute ét in milli second, it is typically traceard of times, and thus a processor is said to be able to execute so unit, which happend to be based on the simply nears is MIPS. One argut think that MIPS simply nears many sneystones presecond. millions of instruction per mond, but actually the consum all of the lieur is based on a somewhat more complex notion The use and validity of buchwark data is a subject of quat controversy. There is also a clear need for senchmarks that desence performance of eared ded processor.

b. Design a Finite State Machine using a simple microprocessor. (6) Answer:

5) Design a Finite state M/c using a simple elf. PC20 Resul IR = MEPC] Fetch PC = PC+1 Decode RFERNJ=[M][dig] 0000 Mov 1 > To Fetch 000 M Edia] 2 RF[an] Mov 2 > To fetch 0010 M[an] = RF[am] Mov 3 > To Fptch 0011 KF[2n] 2 imm To Fetch 0100 RF [2m] = RF[2n]+RF[2m] Adol. To Fetch RF [Rn] z RF[In] - RF[Im] 0101 Sub To Fetch PC = (RF(1)=0) ? 221: PC 0110 JZ To Fetch. A General Purpose plocesser is really just a singleprocessoe whose puepose is to process instanctions stand in a plogram memory. Therefore, we can debign a general using the single purpose processol purpos processor , while real MP design keenige described in intended for mass production are more commanly deepgud using custous method where than the general technique of missection, using the general helmique here vier prove a useful excercise that will identify the basic unity b/w single pulpose & gueral fuppse processor. 17 © IETE

**DEC 2015**

Suppose me want to design a genreeal puepe processor. we can begin by creating the FSMD shows in Fig. which describes the desired processes behavior. The FSMB declares several variable for thorage a 16- bit pregram counter PC, a 16 bit instruction regiter IR. a 64K × 16 bit meanery M. and 16×16 bit register file KF. The sucde state does nothing but adds the extra cycle necessary for IR 10 get updated some cans then read it on an are Fach are leaving the seede state detects a particular institution apcode causing a trans b'an to the corresponding execute state for the opcod. Each execute state, lik Mov 2 Add and Jz, carries out the annual instruction apleation by moving data 5/4 storage devices, nodifying data es updabing PC.

c. Give the features of SoC design. Answer: (6)

A Ston Q'C feature of Soc Design: Soc (system on chip) is an integrated crust (10) that integrates all components of a computer or other electronic system into a single chip. It may contain digital, analog, mixed-signal, and affe. radio-pequency functions. all on a single chip substrate. Socs and very common in the mobile electronices market because of Heir low power consumption. A typical application is in the oxer of embedded system. Design Elows; Jarrel Development of S/W IP Block. purviel pevelopment of HW IP Block Gennic Specify Selware IP Mold Generic Systemon HID IP CUP Block Archickure Partition platform . HIW SIW V PEPLICA Enlegence Sofume Thegrake Affertation profic. mole IP EPMalel Specific specific HIN IP Block BLOCK Lowlove soffwore Funchonul simult Simulation Hardware and low level Solware Application Physical S/W Developmon Design H/w-S/W Software Prototype Very frention Test IC fabrication FCL - abrah ell.

| Q.3 a. What are the different types of ROM? Explain read/write mechanism of EEPROM.                                         |

|-----------------------------------------------------------------------------------------------------------------------------|

| Answer:                                                                                                                     |

| - (R) Types of Rom                                                                                                          |

| Memoryes in the Rom family are distinguished by the methods                                                                 |

| Nemories in the Rom family are distinguished by the methods<br>used to work new data to them Cusually called programming or |

| burning) and the number of among an be substance                                                                            |

| This cause fication stelleds the merelition of Rom device from                                                              |

| hand - wired to one - time programmable to escusable and projection                                                         |

| The common dealure across all these devices is they upper                                                                   |

| retain data and programs forever, even when power is removed.                                                               |

| 1) The very first Rome Work hard wired daviles that Contained a                                                             |

| reprogrammed set of data or instructions. The contents of the north                                                         |

| had to be specified before this production, so the actual court                                                             |

| (ould be used to avoiange the tounsistons inside the conf.                                                                  |

| Haydisird, memories are still used, through meg are we                                                                      |

| Colles masked Roms to distinguish them guers and g                                                                          |

| of ROM. The main advontage of a maykel Rom is a low                                                                         |

| Dera Luckion (Ost                                                                                                           |

| The cast is low when hundreds of thousands of copies of the<br>some Rom are required.                                       |

| some Rom are required.                                                                                                      |

| a is i have if the programmazas we first                                                                                    |

| & Another types in her warder money state. If you were to                                                                   |

| (2) Another types of kerr & the programmed state. If you were to<br>is purchased in an unprogrammed state. If you would     |

| took a me conterns of an 10                                                                                                 |

| see that all the buts are 18. The process of weithing your called                                                           |

| Jake to the PROM involves a special piece of equipment Caller                                                               |

| a device programmer, which worthes data to the device of                                                                    |

| a Levice programmer, which weittes data to the device by applying a higher. Than normal voltage to special input pin        |

| of the chip. Once a prom has been programmer in my                                                                          |

| its contents can never changel. In the coce of data stores                                                                  |

| in the prom must be changed the chop must be ascarded                                                                       |

| © iete 20                                                                                                                   |

and suplaced with a new one. As a subsult, PROMS are also Janown as one-time programmable (OTP) deviles. 3) EPROM (crossable and bogrommable from) is programmed in exactly. the same manner of a PROM. However, EPROMS can be evaled and suprogrammed supeakedly. To exase in EPROM, simply expose the device to a strong source of ultraviolet light. By doing this you estentially nesct the entire clip to its initial - unprogrammed The exasure fine of an EPROM can be anything from 10 to 45 minutes Which can make soft-wave debugging a slow protess. Though more expensive than PROMS, their ability to be suprogrammed male EPRoms a common feature of the embedded software development and besting process meny years. It is now relatively size to see EPROMUL in embelled systems, as they have been supplanted by newer technologies Real posite mechanism of EEPROM: ECPROM is internelly similar to an EPROM, but with the erasc operation accomplished electrically. Additionaly, a single byte within an EEPROM conbe exased and siewitten. One waithen, the new John will menan in the device forever -or at least until it is electrically crosses. One, tradeoff for this improved Junctionality is higher cast; another is that typically EEPhom is good for 10,000 to 100,000 white (yelds. El PROMS are available in a standard parallel mer feic as well as a several interface. In many design, the inter-IC (It) or sevial Peropheral Interface (SPS) buses are used to communicate with sever coppon devices.

b. Discuss common memory problem and possible solutions. Answer: (6)

(b) Common memory problems and solutions. AISW A more common source of memory problems is the circuit bouch . Fyprial crust beard problems are:-O Broblems with the wowing b/w the protessor and memory devices. Ausing Memory Chip. O Improperly inserted memory chips. These are the problems that a good memory test algo suthing Should be able to detect. Such a test should also be able to detect catastrophic memory failures without specifically looking for them. So let's discuss circuit board problems in more detail. Electrical Wiring problems: An electrical wining problem could be caused by an error in design or production of the board or as the moult of damage received after manufacture. Each of the sorres that connect the Memory device to the praction is one of there types. · Addrew signal · Data signal. · Control signal. The altres and data signals select the memory Location and bransfor the data respectively. The control signals tell the memory device whether the processor works to sheat or write the location and precisely when the data will be transfermed. Unfortunately one or more of these where could be improperly stould or domaged in such a voy that it is either shorted or open. shorting is often caused by a bit of solder splach, whereas an open wire could be caused by a broken trail. Both cases are illustrate in fig.

| Memory<br>Memory<br>Prolessor<br>Prolessor<br>Shorke Lare.<br>Memory.<br>Prolessor<br>Open Wire.<br>Memory.<br>Prolessor<br>Open Wire.                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problems with the electrical connections to the processor will Cause<br>the memory device to belove incorrectly. Data might be Coorrupted<br>when it's stored, stored at the wrong address, or not stored at<br>all. Each of these symptoms can be explained by wiring problems<br>on the data, address, and control signals, respectively.                                                                                      |

| If the problem is with a data signal, several data bits might<br>appear to be " stuck together". Similarly, a data but might be<br>either "stuck high " (alway 1) or "stuck low" (alway 0). These problems<br>can be detected by writing a sequence of data values designed to<br>can be detected by writing a sequence of data values designed to<br>test that each data pin can be set to 0 and I, independently               |

| In an address signal has a weithing powerlap. The contents<br>of two memory locatons might appear to overlap. In other<br>of two memory locatons might appear to overlap. In other<br>words, data weither to one address will instead overwork<br>words, data wither to one address will instead overwork                                                                                                                        |

| the contents of another and the processor.<br>different from the one selected by the processor.<br>Another possibility is that On of the control signal is shorked<br>or open. Although it is theoretically passible to develop specific<br>or open. Although it is theoretically passible to develop specific<br>tests for control signof problems, it is not passible to describe<br>a general test that covers all platforms. |

**CT74**

**DEC 2015**

A 15/1.) Missing Memory chips A mussing memory chip is clearly a problem that should be detected. Unfortunately because of the capacitive nature of unconnected elatrial wires, some memory tests will not detect this periblem. for example, suppose you decided to use the following test algorius While the value 1 to the first Location in memory, verify the Value by greating it back, white I to the second location, verify the value, while 3 to the third Location, verify and SO On. Be cause each great occurs immediately after the Corresponding would, it is possible that the data sear back sepresents nothing more than the vallage semaining on the Later bus from the previous write. If the date is near back quickly, it will appear that the data bus from the previous Would. If the data is shad quickly, it will appear that the date has been correctly stored in memory, even though there is no memory chip at the ather end of the bur? To detect a missing memory chip, a better test must be used. Instead of performing the verification stead immediately after the crossponding white, perform several consecutive whites followed by the some number of consecutive steads. for example Write the value I to the First location, write the value 2 to the second location, while the value 3 to the third location, and then vorify the data at the first location, the second Location, and so on. If the data values are unique, the missing chip will be detected : the figust value great back will correspond to the last value witten (3) suther then to the first ()

Improperly inscorded chips. If a memory chip is present but improperly inserted, some pine On the memory chip will either not be connected to the circuit board at all or will be connected at the wrong place. These pins will be part of the data bus, ad snew bus, or control wiring. The system will usually behave as though there is a wiring problem or a missing chip. So as long as you test for wiring problems and missing Chips, any improperly inserted chips will be detected automatically Before going on , Let's quickly seriew the types of memory problems we must be able to detect memory chip only savely have intomat errors, but if they do, they are typically catastrophic in nature and should be detected by any test. A more common source of problems is the circuit board, where a wiring problem can occur or a memory chip might be missing or improperly inserted. other memory problems can occur, but the ones described here are the most common and also the simplest to test in a generic way.

c. Give the issues that need to be considered when upgrading software using flash memory. (6)

Answer:

Aufum

(2)

In Issues that Need to be considered when upgrading software using · Flash memory.

**EMBEDDED SYSTEMS**

Flash memory affers advantages over ather types of memory. Systems with flash memory can be updated in the field to incorporate new features or bug fixes discovered after the product has been Shipped. This can eliminate the need to chip the Unit back to the manufacturer for Software repgrades. There are several usives that need to be considered when upgrading software for units in the field. Limit downtime :-

The timing of the upgrade should take place during downtime. Since The unit will Brobabily not be able to function at its full Capacity during the upgrade, you need to make sure that the Unit is not performing a critical task. The costomer will have to dictate the most convenient time.

Power failure

How will the Unit recover should power be semoved while the upgade is tasking place? If only a few bytes of the application image fave been programmed into flash when the power is removed, you need a way to determine that an error occurred and prevent that code from executing. A solution may be to include a loader that cannot be exased because it resides in protected flash sectors. One of the boot tasks for the leader is to check the flash memory for a valid application image . gj a valid image is not present, the loader needs to know how to get a valid image onto the bound, was serial port, network, or some other means. Another solution for power failures may be to include a

flash memory device that is large enough to store two application images. The current Image and the all Image . When new firmware

is available, the old image is overwouthen with the New And software; the current image is left alone. Only after the image this been programmed properly and verified does it become the current image. This technique ensures that the unit always has a valid application image to execute should something bad tappen during the upgrade procedure. Upgrade Code execution:-

From which memory chip will the saftware execute during the evase and programming of the new saftware? The software that downloads the image may be able to run from that memory; however, the code to erase and improgram a flash chip might need to be run from another memory device.

Device timing requirements: It is important to understand the fiminy requirements of the program and exase cycles for the particular flash device. It is best to make sure all data is present before storting the programming cycle. You would not wont to short programming the device and then be caught waiting for the rest of the new software to come in over a network connection. The device may have timing limits for program and erase cycles that cause the device to scoret back to read mode if these limits are exceeded. The flash device deriver would fail to work the data if this occurs.

Software image validity: It is important to validate the image that is written into the Elest. This will ensure that the software is received into the Unit Correctly. The CRC algorithm presented earlier in this chapter may be suffrient to satisfy the validity of the upgrade software. Security.

If security of the image is an issue, you may need to find an algorithm to digitally sign and for encrypt the new software. The validation and decryption of the software would then be performed prior to programming. **CT74**

Q.4 a. Explain communication basics for embedded system with a simple example of bus structure, read protocol and write protocol. (6)

Answer:

Ans Communication basics for embedded system with a simple Erample we begin by interducing avery basic comprunication example between a processed and a meanery, saw in Fig. shows the bus structure, or the nices connecting the processor and he mewary, The line ed/wy indicates whether the processor is reading or weiting . An enable line is used by the processor wishes to carry out me reader meste. Twelve address line addr. Indicate the neurony address that processor mightes to read or write . Twelve address lines adde . indicate the memory address that the processor neights to read or write. Eight data lines data are set by ble processor when winning or set sy the memory when the processor is reading. Fig(b) describes the read protocol over these men; The processor set rd " we to b, places avalid dates on the data lines. Fig () Show a meite protocal : the processor sets rd'/me to 1, places a nation address on adde, places data and als, and sheaks enable, caupine the memory to store the data. This very simple example brings up several points that we know describe. Wises may be undirectional, maning they traismt in only one direction, as did relifue, enable, and adde, on they may be bidirectional, meaning they transmit in two dilections, though in only are directions at a time as did date . I set of mines with the land for is hypotally deawn as a twick line and for as a lime with a small angled line drawn theory it as mas precase with adds and data

The teem but can refer to a set of weres with a single fan wety in a communication. De example me can refer to the "address bus" and the date bus in the above example. The term bus can also seeks to the entire collections of mees used for the communication along hits the comm. probable over those wires. Both user of the term are common and are often used in conjunctions mites one another. For example, me Bay "mat the processor's but consist of an address bus and a data bus . A proto cal describes the sules for consumicating over tuber mines. me deal primarily miter low level hardward protocol in this chepter! while higher-level protocol, like IP (Internet Peolow) can be built an lop of these protocols, using alayered appeach. 2d/Wz Memory Processer enable. adde [0-11] data [0.7] Bus (a) 20 Wh ed we chable enable. adde. a dde dater data teetup tread tweite (6) 2)

The diagean shows that the high enable ene trigger the heavery to put data on the data wires after tread. Note that a timing diagray septa time. sents control lines, like red/we and enable, as either being high orlaw, while it sep. data lines, like adde andabter, either as being invalid avalid, using a single horizoutal line of two horizoutal lines, respectively. The achiel value of data lines is not normally relevant when descerbing a platoed, so that value is typically not chown. In the above protocol, the control line enable is active high, nearing that a I on the enable eine teigger sur data transfer i her wany protocol, control lines are instead active law, rearing that a O on the line trigger the transfer.

b. Discuss embedded processor interfacing and explain port-based I/O and busbased I/O. (6)

Answer:

8 Microprocessor Interfacing ! 1/0 Addressin m Port and Brus - Based 1/0 A nicroprocessoe may have ten or hundred of prins, many of which are caultal prins, such as a prin for clack, input and another input pin for resetting the lep. Many of the other pins are used to communicate data to and from the up. which we call processor 1/0. There are hus common methods for using to support 110; port-saled 1/0 and bus pasid 1/0 1) In port pand 110; also isnass as paereled. 110 a portcan be discilly had and weiten by processor materia-tions just like any other register in the up; in fact, the

part is usually connected to a dedicated sigis he. in the tel , For eg, courside au 8-bit port maned PO. A C-language programmer way nieite to Po using an instruction like : Po = 255, which would at all eight pine to is. In this case, the C coopsiler manual mould have defined to as a special variable that would automatically be mapped to the register Po during compilation. conversely, the programmer night Read the value of a port PI being nuitters by come other durice by typing concluing like a = P1. In some UP, each sit of a port can be configured as imput a output by meiting to a configuration register called clo. To set the high-older four sits to imput and the have - erelie four sits to output, me night ray: CPO=15. This wester 0000/111 to CPO registre, where a 0 means imput and a I means output Poets all often bit-addressable, meaning mat a programmer consead or unite specific site of the poet. For example, one night say : x = PO. ? giving se the value of the number 2 pin of poet Po. (ii) In bus-based 1/0, me up has a set of address, data, and control ports corresponding to bus lines, and uses the bullor to accuss nearony as well as peripherale. The UP has the bus protocol will in to its hardmare. Specifically, the settmare does not implement the pielocal but nearly executes a single

instructions that in her caules the hardward to

consider the access to the purpheeal as I/O, but

verite er reel data over me bus. We normally

32

onthormally combided the access to meaning as I/O I -since the nearby is considered more as a partof the up. A Systems may require parallel I/O (port-based I/O), but a UP may only support bus - based I/O In this case, a parallel I/o preipheral may be used, as illustrated Fig. The peripheral is connected to the system bus on the other side, consisting just of a set of data line. The ports are connected to register invide the peripheral, and the MP can read and write most register in order to read and meite me ports. Even when a up support poet-based 2/0, we may requéer more poets than are available. In this case. a parallel I/o peripheral can again be used, as illustrated in Fig. The UP has four parts in this ea. one of which is need to interface with a parallel. I/o paipneed, which itself has there parts Thus We have extended the number of available parts firm pour & six. Using a prei prieal in this regimer is often referred to as extended parallel I/O. > Porto Processor Mennery Processor > Port1 System Bus > Port2 Parallel I/0 Parallel I/O peripheral peripheral. Porta Ports Portc PoetA PoetB Poetc (a) (b)

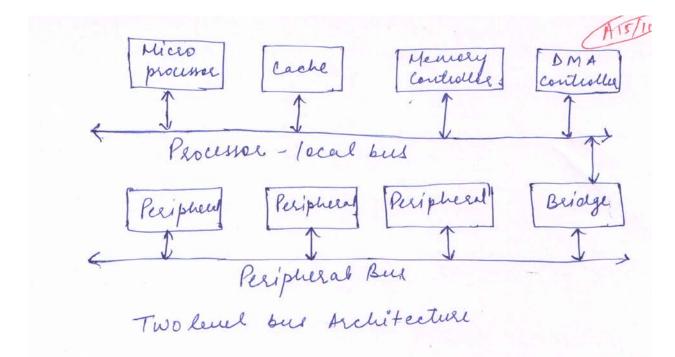

c. Draw and explain two-level bus architecture. Answer: (6)

A microprocessor based en bedded systems will have menserous type of consumications that must take place Varying In their prequencies and speed requirement The wort frequent and high speed computinication will littly be between the UP. & its peripherals, like a CART, we could try to implement a single high speed bus for all the consynication, but this approach has several disadvantagee. First, it require each periphical. to have a high-speed bus inkeface. Since a periphalmay not need such high-speed communication, having such our interface, way result incates, power commutin and cost. Second, since a dign speed bus mill be very processor -specific, a peripheral miter an interface to that but may not be very portable. Third, having to wany peripereals on the bus way result in slower bus. Therefore, we often design septions with two level of buses: a high speed precesser local bus and a lower epied periphical bus, The processor local bus typically connects the up, cache, memory intollers and certain high-speed co-processors, and is processor specfic. It is usually mide, as wide as a meandary word. The purpheral bus connects those processors that do not have fast processor local bus access as a hop priority, but latuer emphasize partabolity, low power, as low gate court. The prespecal bus is typically an inducting standard bus, such as ISA or PCI, thus supporting portability of the preipherals. It is after naven and les server than a process of local bul thus requering ferrer mins, fewer gates and less

(6)

# Q.5 a. What is scheduler? Explain Priority based scheduling. Answer:

Now that we have a priority-based context switching mechanism, we have to determine an algorithm by which to assign priorities to processes. After assigning priorities, the OS takes care of the rest by choosing the highest-priority ready process. There are two major ways to assign priorities: *static* priorities that do not change during execution and *dynamic* priorities that do change. We will look at examples of each in this section.

## 6.3.1 Rate-Monotonic Scheduling

**Rate-monotonic scheduling (RMS)**, introduced by Liu and Layland [Liu73], was one of the first scheduling policies developed for real-time systems and is still very widely used. RMS is a static scheduling policy. It turns out that these fixed priorities are sufficient to efficiently schedule the processes in many situations.

The theory underlying RMS is known as *rate-monotonic analysis (RMA)*. This theory, as summarized below, uses a relatively simple model of the system.

- All processes run periodically on a single CPU.

- Context switching time is ignored.

- There are no data dependencies between processes.

- The execution time for a process is constant.

- All deadlines are at the ends of their periods.

- The highest-priority ready process is always selected for execution.

The major result of RMA is that a relatively simple scheduling policy is optimal under certain conditions. Priorities are assigned by rank order of period, with the process with the shortest period being assigned the highest priority. This fixed-priority scheduling policy is the optimum assignment of static priorities to processes, in that it provides the highest CPU utilization while ensuring that all processes meet their deadlines.

Example 6.3 illustrates RMS.

### Example 6.3

#### Rate-monotonic scheduling

Here is a simple set of processes and their characteristics.

| Process | Execution time | Period |

|---------|----------------|--------|

| P1      | 1              | 4      |

| P2      | 2              | 6      |

| P3      | 3              | 12     |

Applying the principles of RMA, we give P1 the highest priority, P2 the middle priority, and P3 the lowest priority. To understand all the interactions between the periods, we need to construct a time line equal in length to hyperperiod, which is 12 in this case.

All three periods start at time zero. P1's data arrive first. Since P1 is the highest-priority process, it can start to execute immediately. After one time unit, P1 finishes and goes out of the ready state until the start of its next period. At time 1, P2 starts executing as the

highest-priority ready process. At time 3, P2 finishes and P3 starts executing. P1's next iteration starts at time 4, at which point it interrupts P3. P3 gets one more time unit of execution between the second iterations of P1 and P2, but P3 does not get to finish until after the third iteration of P1.

Consider the following different set of execution times for these processes, keeping the same deadlines.

| Process | Execution time | Period |

|---------|----------------|--------|

| P1      | 2              | 4      |

| P2      | 3              | 6      |

| P3      | 3              | 12     |

In this case, we can show that there is no feasible assignment of priorities that guarantees scheduling. Even though each process alone has an execution time significantly less than its period, combinations of processes can require more than 100% of the available CPU cycles. For example, during one 12 time-unit interval, we must execute P1 three times, requiring 6 units of CPU time; P2 twice, costing 6 units of CPU time; and P3 one time, requiring 3 units of CPU time. The total of 6 + 6 + 3 = 15 units of CPU time is more than the 12 time units available, clearly exceeding the available CPU capacity.

Liu and Layland [Liu73] proved that the RMA priority assignment is optimal using critical-instant analysis. We define the *response time* of a process as the time at which the process finishes. The *critical* instant for a process is defined as the instant during execution at which the task has the largest response time. It is easy to prove that the critical instant for any process P, under the RMA model, occurs when it is ready and all higher-priority processes are also ready—if we change any higher-priority process to waiting, then P's response time can only go down.

We can use critical-instant analysis to determine whether there is any feasible schedule for the system. In the case of the second set of execution times in Example 6.3, there was no feasible schedule. Critical-instant analysis also implies that priorities should be assigned in order of periods. Let the periods and computation times of two processes P<sub>1</sub> and P<sub>2</sub> be  $\tau_1$ ,  $\tau_2$  and  $T_1$ ,  $T_2$ , with  $\tau_1 < \tau_2$ . We can generalize the result of Example 6.3 to show the total CPU requirements for the two processes in two cases. In the first case, let P<sub>1</sub> have the higher priority. In the worst case we then execute P<sub>2</sub> once during its period and as many iterations of P<sub>1</sub> as fit in the same interval. Since there are  $\lfloor \tau_2/\tau_1 \rfloor$  iterations of P<sub>1</sub> during a single period of P<sub>2</sub>, the required constraint on CPU time, ignoring context switching overhead, is

If, on the other hand, we give higher priority to  $P_2$ , then critical-instant analysis tells us that we must execute all of  $P_2$  and all of  $P_1$  in one of  $P_1$ 's periods in the worst case:

$$T_1 + T_2 \le \tau_1.$$

(6.5)

**EMBEDDED SYSTEMS**

There are cases where the first relationship can be satisfied and the second cannot, but there are no cases where the second relationship can be satisfied and the first cannot. We can inductively show that the process with the shorter period should always be given higher priority for process sets of arbitrary size. It is also possible to prove that RMS always provides a feasible schedule if such a schedule exists.

The bad news is that, although RMS is the optimal static-priority schedule, it does not always allow the system to use 100% of the available CPU cycles. In the RMS framework, the total CPU utilization for a set of n tasks is

$$U = \sum_{i=1}^{n} \frac{T_i}{\tau_i}.$$

(6.6)

The fraction  $T_i/\tau_i$  is the fraction of time that the CPU spends executing task *i*. It is possible to show that for a set of two tasks under RMS scheduling, the CPU utilization *U* will be no greater than  $2(2^{1/2} - 1) \cong 0.83$ . In other words, the CPU will be idle at least 17% of the time. This idle time is due to the fact that priorities are assigned statically; we see in the next section that more aggressive scheduling policies can improve CPU utilization. When there are *m* tasks with fixed priorities, the maximum processor utilization is

$$U = m(2^{1/m} - 1). (6.7)$$

As *m* approaches infinity, the least upper bound to CPU utilization is  $\ln 2 = 0.69$ —the CPU will be idle 31% of the time. This does not mean that we can never use 100% of the CPU. If the periods of the tasks are arranged properly, then we can schedule tasks to make use of 100% of the CPU. But the least upper bound of 69% tells us that RMS can in some cases deliver utilizations significantly below 100%.

The implementation of RMS is very simple. Figure 6.12 shows C code for an RMS scheduler run at the OS's timer interrupt. The code merely scans through the list of processes in priority order and selects the highest-priority ready process to run. Because the priorities are static, the processes can be sorted by priority in advance before the system starts executing. As a result, this scheduler has an asymptotic complexity of O(n), where n is the number of processes in the system. (This code assumes that processes are not created dynamically. If dynamic process creation is required, the array can be replaced by a linked list of processes, but the asymptotic complexity remains the same.) The RMS scheduler has both low asymptotic complexity and low actual execution time, which helps minimize the discrepancies between the zero-context-switch assumption of RMA and the actual execution of an RMS system.

```

/* processes[] is an array of process activation records,

stored in order of priority, with processes[0] being

the highest-priority process */

Activation_record processes [NPROCESSES];

void RMA(int current) { /* current = currently executing

process */

int i;

/* turn off current process (may be turned back on) */

processes[current].state = READY_STATE;

/* find process to start executing */

for (i = 0; i < NPROCESSES; i++)</pre>

' if (processes[i].state == READY_STATE) {

/* make this the running process */

processes[i].state == EXECUTING_STATE;

break;

}

```

#### FIGURE 6.12

C code for rate-monotonic scheduling.

## 6.3.2 Earliest-Deadline-First Scheduling

*Earliest deadline first (EDF)* is another well-known scheduling policy that was also studied by Liu and Layland [Liu73]. It is a dynamic priority scheme—it changes process priorities during execution based on initiation times. As a result, it can achieve higher CPU utilizations than RMS.

The EDF policy is also very simple: It assigns priorities in order of deadline. The highest-priority process is the one whose deadline is nearest in time, and the lowest-priority process is the one whose deadline is farthest away. Clearly, priorities must be recalculated at every completion of a process. However, the final step of the OS during the scheduling procedure is the same as for RMS—the highest-priority ready process is chosen for execution.

Example 6.4 illustrates EDF scheduling in practice.

b. Discuss some of the important criteria used in making an RTOS selection. (6) Answer:

| (b) Important Criteria uses in making an RTOS selection:                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor support:<br>The processor is typically the first choice in the hardware design on<br>a project. Most KTOSES support the popular processors used in<br>embedded systems. If the processor used on your project is not<br>supported, you need to determine. whether porting the RTOS to<br>that processor is an option or if it is necessary to choose a<br>different RTOS. Porting an RTOS is not always trivial. |

| Real time characteristics:<br>We have allocady covered the sceal-time charactersticks of on RTOS,<br>Which include Interrupt latency, context switch time, and the<br>Which include Interrupt latency, context switch time, and the<br>execution time of each system call. These are technical contexia<br>that are inferent to the system and cannot be changed.                                                          |

| Budget Constraints:<br>RToses span the cast spectrum from open source and<br>kToses span the cast spectrum from open source and<br>developer                                                                                                                                                                                                                                                                               |

| orbyalty gree to too of each unit shipped. You need to<br>seat plus moyalhes for each unit shipped. You need to<br>understand what your casts are in both cases. Open source<br>might mean no upfiont casts, but there might be casts<br>associated with getting support when needed. You also need to<br>understand the triensing details of the KTOS you choose.<br>Memory usage:                                        |

| Memory usage:<br>Clearly, in an embedded environment, memory constraints are<br>a frequent concern. A few RTOSEs can be scaled to fit the                                                                                                                                                                                                                                                                                  |

Smallest of of embedded systems. For example, by removing features to create a smaller botprint. others require a minimum set of resources comparable to a low-end PC. It is important to beep in mine the potential need to change on RTOS in the Fature, when memory is not a plentiful or carly here to be reduced.

Device drivers and software components:-

The device derivers included with an RTOS Can aid in keeping the development on schedule. This neduces the amount of Code. you need to develop for panhalar perspherals. Many RTOSES support the common devices found in embedded system. If additional features are needed, such as networking support, graphics libraries, web interfaces, and filesystems, an RTOS might include these and lave the code aloready integrated and tested. Some RTOS might require more fees for lung these added features.

Technical support:

This may include a number of incidents or a period of phone support. Some Rioses require you to pay an annual fee to maintain a service contract. for open source Rioses, an open forum or mailing dist might be provided. If more specialized support is needed, you'll have to search around to see what is avail able. Popular open source Riosus have companies dedicated to Providing support. Tool compatibility:

Make Sure the KTOS works with the assembler, computer, linker, and debuyger you have aloready obtained . If the RTOS does not support tools that you or your team are familiar with , the lawrning curve will take more time.

c. Explain interrupt handling in embedded system. (6) Answer:  $(\mathcal{C})$ Ans Interrupt handling in embedded system: There are several usues you need to be aware of when handling interrupts in embedded system that we en operating system including: Intermupt priority:-Interrupts have the highest pricesity in a system reven higher than the heghest operating system task. Interrupts are not Scheduled the ISR executes outside of the operating system's scheduler. Disabling interrupts: Because the operating system code must guarantee its data structures integrity when they are accessed, the operating system desables interrupts during operations that alter internal Operating system date, such as the ready dist. This increase the interrupt latency. The responsiveness of the operating system comes at the price of longer interrupt latency. When a task disables interrupts, it prevents the scheduler from doing its job. Tasks should not disable interrupts on their own. Interrupt stack Some operating systems have a separate stack space for the execution of ISRs. This is important because, if interrupts one stored on the same stack as negular tasks, each tasks Stade must accommodate the worst-case interrupt nesting Scenario . Such large stacks increase RAM sequirements across all n tasks. Signaling tasks: Because Isks execute outside of the Scheduler, they are not allower to make any operating sysk n Calls that Can block. for

(6)

block for example, an ISR that handles the bare minimum processing of the interrupt. The idea is to beep the ISR short and quick. The second part is handled by a DSR. The DSR handles the more extensive processing of the interrupt event. It sums when task scheduling is allowed; however the DSR still has a higher priority than any task in the system. The DSR is able to signal a task to perform work toggered by the interrupt event.

Q.6 a. Discuss system synthesis and hardware/software co-design. Answer:

**DEC 2015**

Ans (a) System Synthesis and Hardware / Software Codesign. System synthesis converts multiple processes into multiple processors. The berm system here rejers to a Collection of processors. System synthesis involves several tasks. Transformation is the task of newvitting the process to be more amenable to synthesis. for example, a designer may have described some behavior using two processes . but analysis night show that there two processes are really exclusive to one another and thus could be merged into one process. like wise, a large process night actually consist of two indepedent operations that could be done concurrently, so that process could be divided into two processes. after common transformations include procedure inlining and loop unralling. Allocation is the task of selecting the number and types of processors to use to implement the processes. A designer night choose to use an 8-bit general-purpose processor along with a single - purpose processor. Alternatively, the designer night use a 32-bit general - purpose processor. And 8-bit general purpose pracesor, and multiple single - purpose pro censors. Allocation achievely includes selecting processors, memories and bases. Allocation is essentially the design of the system architecture. Partitioning is the task of mapping the processes to processors. one process can be implemented on multiple processors, and Multiple projesses can be implemented on a single projessor. Libewise variables must be partitioned among memories and communications among buses.

Scheduling is the task of selectining when each of the multiple processes on a single processor will have its chance to execute on the processor take wise, memory accesses and bus communications must be scheduled. These tasks may be performed in a variety of orders, and storation Among the tasks is Common. System synthesis, like all forms of synthesis, is driven by constraints. A typical set of constraints dictoles that certain performance. requirements Must be met at minimum cost. In such a situation, system synthesis might seek to allocate as much behavior as possible to a general - purpose processor, since a Gyp may provide for low Cost, Elexible implementation. A minimum number of single poppese processors might be used to neet the performance requirements. Systen synchresis for general - purpose process only has been oriound for a few decades, but hasn't been called system synthesis. Name like multiprocessing, parallel processing, and shear time schelding have been more Common The maturation of behavioral synthesis in the 1990s has enabled the Consideration of single purpose processor during the allocation and partitioning tasks of system synthesis. This the term Hardware / software Codesign has been used extensively the research community, to highlight research that tocuses in on the Unique requirements of such Simultaneous consideration of both handware and software during synthesis,

b. Explain formal verification and simulation of hardware/software co-design. (6) Answer:

(b) formal verification and simulation of hand ware and software co-design verification is the task of ensuring that a design is correct and complete. Correctness means that the design implements its specification accurately. Completeness means that the design's specification described appropriate output responses to all relevant input sequences.

The two main approaches to vovification that onalyzes a design to prove or disprove certain properties. We might seek to formally verify correctness of a particular design step, such as Verifying that a particular Structured description correctly implements a particular behavioral description, by proving the equivalence of the two descriptions for example, we might describe an ALU behaviorally and then create a structural implementation loing gates. We can power the correctness of the structure by dearing a Boolean equation for the subjuts, creating a truth table for these equation, and Showing that this truth table is identical to the table created from the original behavior. Alternatively, we might seek to formally verify completeness of a behavioral description, be proving for mally that certain situations always or never occur. for example we move prove that for of an elevator controller, the elevator door can never be open while the elevator is Moving by deriving the conditions for the door being open and Showing that these conditions conflict with those for the

The more common approach to verification is simulation. formal verification is a very hard problem. and as such best been limited in practice to either smaller designs or to verifying Only certain key properties. Instead by far the Mast Common approach to verification in produce is simulation. Simulation is an approach in which we creak a model of the design that can be executed on a computer. We provide sample input values to this model, and check that the adjust values generated by the model match our expectations, for example use can verify the correctness of an ALU by providing all publishe input combinations. and checking the ALU culture for correct stessels, which we of course fave to compute using other Means.

Compared with physical implementation Simulation fas Several alventage with suspect to testing and debugging a system. The Two nost important advantages are excellent controllability and Observability. Controblability is the ability to control execution of the system. A designer Can control time as well as data value.

- · Simulation Could take much time for system with Complex external environments . A designer may spend more time modeling the external environment than the system itself.

- · Simulation speed can be quite slow compared to execution of physical implementation.

c. Give the steps of development of process model. Answer:

(6)

Steps Design Process Models:-A designer must proceed through several steps when designing a system we can think of describing behavior as one design step, converting behavior to structure as another step, and mapping structure to a physical implementation as another step. Each step will Obviously consist of numerous substeps. A design process model describes the order in which these step are taken. The torm process leve shall not be confused with the notion of a process in the concurrent process model, nor should it be confused with the IC manufacturing process. Here process refer to the manner in which the embedded system designor proceeds through design Steps.

One process model is the waterfall model,

Suppose a designer has six month to build a system. In the Waterfall model, the designer forst exerts extensive effort, perhaps two months, describing the behavior Completely. Once fully satisfied that the belavior is connect, after extensive behavioral simulation and debugging, the designer moves on to the next step of designing structure. Again, much effort is exerted, perhaps another two months, until the designer is statisfied the structure is correct. finally, the physical. implementation step is carvied out, occupying