Q.2 a. In a base-5 number system, 3 digit representations is used. Find out (i) Number of distinct quantities that can be represented.(ii) Representation of highest decimal number in base-5.

Answer:

digits of representation n = 3digits in base-5 would be -0, 1, 2, 3, 4(*i*) we have relation no of distinct quantities  $= r^n$  $= 5^3 = 125$ So, 125 distinct levels (quantities) can be represented.

(ii) Highest decimal Number can be represented by n(r-1)s i.e., by three 4s.

Since, r=5 So, highest decimal Number = 444

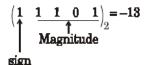

b. In a signed representation given binary string is  $(11101)_2$ . What will be the sign and magnitude of the number represented by this string in signed magnitude, 1's complement and 2's complement representation?

Answer: The number  $N = (11101)_2$ since MSB = 1 the given number is negative.

(*i*) In signed Magnitude MSB denotes sign and rest of the bits represent magnitude. So,

(*ii*) In 1's complement if number is negative (*i.e.*, MSB = 1) then the magnitude is obtained by taking 1's complement of given number.

1's complement of  $(11101)_2 = (00010)_2$

so  $(11101)_2 = -2$  in 1's complement.

(*iii*) In 2's complement if number is negative (*i.e.*, MSB = 1) then magnitude is obtained by taking 2's complement of given number.

2's complement of  $(11101)_2 = (00011)_2$

so  $(11101)_2 = -3$  in 2's complement.

c.Convert the hexadecimal 2AC5.D to decimal, octal and binary.

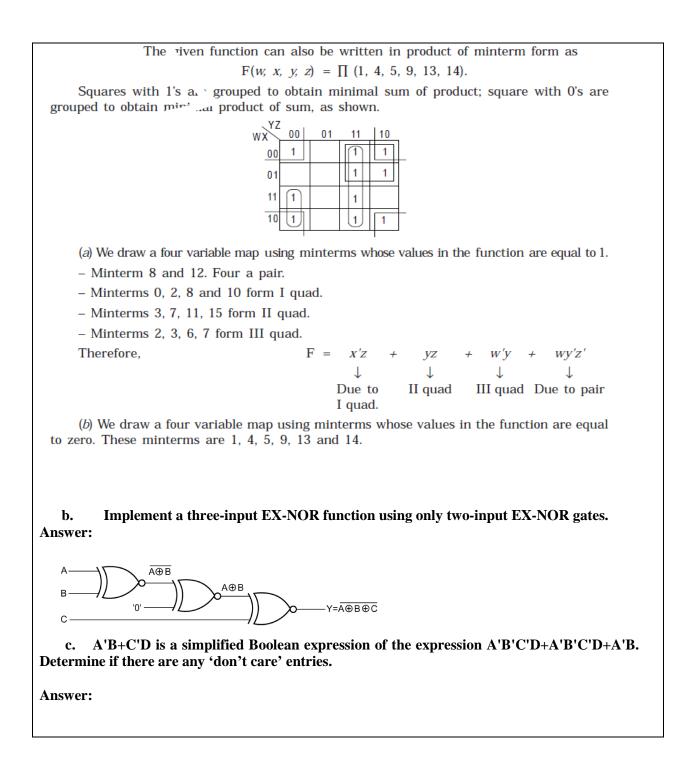

$(2AC5.D)_{16} = (?)_2$ 2AC5 = 0010101011000101 D = 1101  $(2AC5.D)_{16} = (10101011000101.1101)_2$  $(2AC5.D)_{16} = (?)_8$ -10 101 011 000 101 110 1--010, 101, 011, 000, 101, .110, 100,3 0 5 6 4 2  $\mathbf{5}$  $(2AC5.D)_{16} = (25305.64)_8$  $(2AC5.D)_{16} = (?)_{10}$  $2AC5 = 2 \times 16^3 + 10 \times 16^2 + 12 \times 16^1 + 5 \times 16^0$  $= 2 \times 4096 + 10 \times 256 + 12 \times 16 + 5 \times 1$ = 8192 + 2560 + 192 + 5 = 10949  $D = 13 \times 16^{-1}$  $= 13 \times .0625$ = .8125  $(2AC5.D)_{16} = (10949.8125)_{10}$ Q.3a. Obtain (a) minimal sum of product (b) minimal product of sum expression for the function  $F(w, x y, z) = \Sigma (0, 2, 3, 6, 7, 8, 10, 11, 12, 15).$

## DE58/DC58 LOGIC DESIGN

# DE58/DC58 LOGIC DESIGN

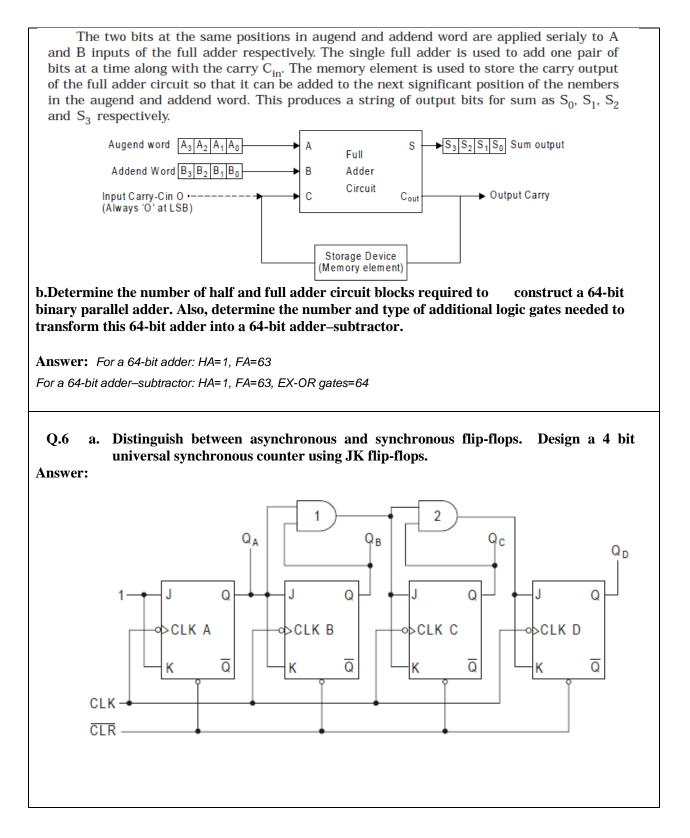

| Present state |   |   | Next state |   |   | Inputs |                |       |       |       |                |

|---------------|---|---|------------|---|---|--------|----------------|-------|-------|-------|----------------|

| С             | В | A | С          | В | A | $J_A$  | K <sub>A</sub> | $J_B$ | $K_B$ | $J_C$ | K <sub>C</sub> |

| 0             | 0 | 0 | 0          | 1 | 0 | 0      | Х              | 1     | Х     | 0     | Х              |

| 0             | 0 | 1 | Х          | Х | Х | Х      | Х              | Х     | Х     | Х     | Х              |

| 0             | 1 | 0 | 1          | 0 | 1 | 1      | Х              | Х     | 1     | 1     | Х              |

| 0             | 1 | 1 | Х          | Х | Х | Х      | Х              | Х     | Х     | Х     | Х              |

| 1             | 0 | 0 | Х          | Х | Х | Х      | Х              | Х     | Х     | Х     | Х              |

| 1             | 0 | 1 | 1          | 1 | 0 | Х      | 1              | 1     | Х     | Х     | 0              |

| 1             | 1 | 0 | 0          | 0 | 0 | 0      | Х              | Х     | 1     | Х     | 1              |

| 1             | 1 | 1 | Х          | Х | Х | Х      | Х              | Х     | Х     | Х     | Х              |

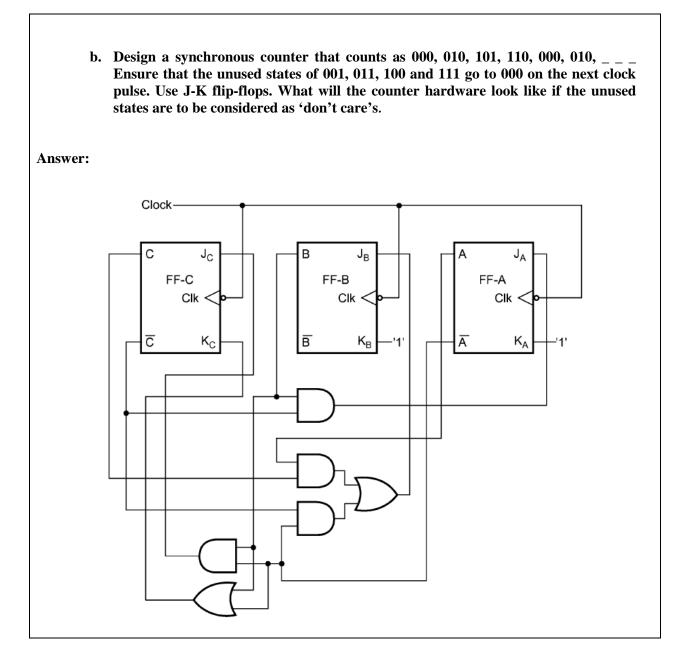

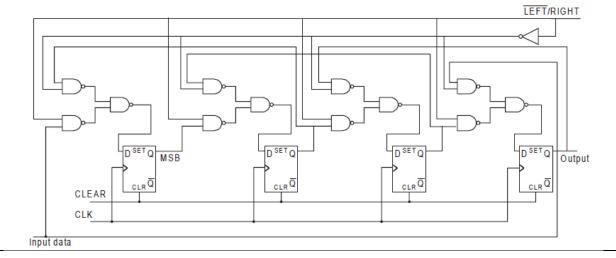

c. Determine the modulus of the presettable counter shown in Fig. 2. If the counter were initially in the 0110 state, what would be the state of the counter immediately after the eighth clock pulse be?

## Answer:

This presettable counter has been wired as a DOWN counter.

- The preset data input is 0110.

- Therefore, the modulus of the counter is 6 (the decimal equivalent of 0110).

- Now, the counter is initially in the 0110 state.

- Therefore, at the end of the sixth clock pulse, immediately after the leading edge of the sixth clock pulse, the counter will be in the 0000 state.

- A HIGH-to-LOW transition at the TCD output, coinciding with the trailing edge of the sixth clock pulse, loads 0110 to the counter output.

- Therefore, immediately after the leading edge of the eighth clock pulse, the counter will be in the 0100 state.

|      | -              | <b>H</b> 0.                      |                        |         | 4 6 11                                   | •                     |                                                          |                             |

|------|----------------|----------------------------------|------------------------|---------|------------------------------------------|-----------------------|----------------------------------------------------------|-----------------------------|

| Q    |                | Use an 8 input                   |                        |         |                                          |                       |                                                          |                             |

|      |                | Y = A'.B'.C'.D<br>A.B'.C.D'+ A.H |                        |         | $\mathbf{C}^{*}.\mathbf{D} + \mathbf{A}$ |                       | $\mathbf{D}^{*} + \mathbf{A} \cdot \mathbf{B}^{*} \cdot$ | <b>C</b> . <b>D</b> +       |

| Ans  | wer:           | A.D .C.D + A.I                   | <b>D.C.D</b> + A.D.    | С.Д.    |                                          |                       |                                                          |                             |

| Alls | wei.           |                                  |                        |         |                                          |                       |                                                          |                             |

|      | Input          | "Addrass"                        | Residues               | 1       |                                          |                       |                                                          |                             |

|      |                |                                  |                        |         |                                          | D                     | - Io                                                     |                             |

|      |                | Ā.B.C                            | D                      |         |                                          | ם                     | -                                                        |                             |

|      | lo<br>I        |                                  |                        |         |                                          | -                     | - 1                                                      |                             |

|      | l <sub>1</sub> | Ā.B.C                            | D                      |         |                                          | 1                     | - l <sub>2</sub>                                         |                             |

|      | 2              | Ā, B, Ĉ                          | $D + \overline{D} = 1$ |         |                                          | 0                     | l_3                                                      |                             |

|      | 3              | Ā.B.C                            |                        |         |                                          | D                     | I4                                                       | -Y                          |

|      | ا4             | A.B.C                            | D                      |         |                                          | $\overline{D}$        | 5                                                        |                             |

|      | l <sub>5</sub> | A.B.C                            | D<br>D                 |         |                                          | 1                     | ۱e                                                       |                             |

|      | le.            | A.B.C                            | $\overline{D} + D = 1$ |         |                                          | 0                     | 17                                                       |                             |

|      | 17             | A.B.C                            |                        |         |                                          | -                     |                                                          |                             |

|      | 17             | R.B.0                            |                        |         |                                          |                       | S <sub>2</sub> S                                         |                             |

|      |                |                                  |                        |         |                                          |                       | ÅĖ                                                       | 3 C                         |

|      |                |                                  |                        |         |                                          |                       |                                                          |                             |

|      |                |                                  |                        |         |                                          |                       |                                                          |                             |

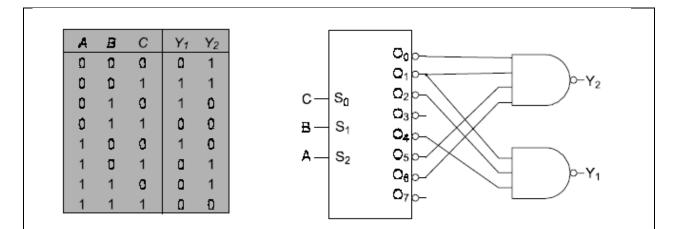

|      | b.             | Implement th                     | e functions de         | fined b | y the fol                                | llowing               | truth tab                                                | le in Fig.3 using a decoder |

|      |                | and NAND ga                      | tes.                   |         | -                                        | _                     |                                                          |                             |

|      |                |                                  |                        |         |                                          | -                     |                                                          | -                           |

|      |                |                                  | Α                      | B       | С                                        | <b>Y</b> <sub>1</sub> | Y                                                        |                             |

|      |                |                                  |                        |         |                                          |                       | 2                                                        |                             |

|      |                |                                  | 0                      | 0       | 0                                        | 0                     | 1                                                        |                             |

|      |                |                                  | 0                      | 0       | 1                                        | 1                     | 1                                                        |                             |

|      |                |                                  | 0                      | 1       | 0                                        | 1                     | 0                                                        |                             |

|      |                |                                  | 0                      | 1       | 1                                        | 0                     | 0                                                        |                             |

|      |                |                                  | 1                      | 0       | 0                                        | 1                     | 0                                                        |                             |

|      |                |                                  | 1                      | 0       | 1                                        | 0                     | 1                                                        |                             |

|      |                |                                  | 1                      | 1       | 0                                        | 0                     | 1                                                        |                             |

|      |                |                                  | 1                      | 1       | 1                                        | 0                     | 0                                                        | J                           |

|      |                |                                  |                        |         | Fig.3                                    |                       |                                                          |                             |

| Ans  | wer:           |                                  |                        |         |                                          |                       |                                                          |                             |

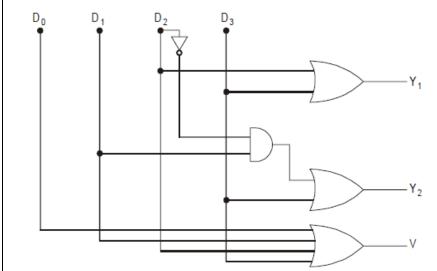

## c. What is priority encoder? Design a 4x2 priority encoder.

#### Answer:

A priority encoder is an encoder that includes priority function. If two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence. To understand priority encoder, consider a 4 to 2 line encoder which gives priority to higher subscript number input than lower subscript number. The truth table is given below.

|       |   | Inp   | uts                   | Outputs |                |                |   |

|-------|---|-------|-----------------------|---------|----------------|----------------|---|

| $D_0$ | Ι | $D_1$ | <i>D</i> <sub>2</sub> | $D_3$   | Y <sub>1</sub> | Y <sub>2</sub> | V |

| 0     |   | 0     | 0                     | 0       | х              | Х              | 0 |

| 1     |   | 0     | 0                     | 0       | 0              | 0              | 1 |

| x     |   | 1     | 0                     | 0       | 0              | 1              | 1 |

| x     |   | х     | 1                     | 0       | 1              | 0              | 1 |

| x     |   | x     | х                     | 1       | 1              | 1              | 1 |

The Xs are don't care conditions. Input  $D_3$  has the highest priority, so regardless of values of other inputs, when this input is 1, the output  $Y_1 \ Y_2 = 11. \ D_2$  has next priority level. The o/p is 10 if  $D_2$  is 1, provided  $D_3 = 0$ , irrespective of the values of the other two lower-priority inputs. The o/p is 01 if  $D_1$  is 1, provided both  $D_2$  and  $D_3$  are 0, irrespective of the value of lower-priority input  $D_0$ . The o/p is  $D_0$  if 00 = 1, provided all other inputs are 0.

A valid output indicator, V is set to 1, only when one or more of the inputs are equal to 1. If all the inputs are O, V is equal to O. and the other two outputs if the circuit are not used.

Now, simplifying using k-map the outputs can be written as :

$$\begin{aligned} &Y_1 = D_2 + D_3 \\ &Y_2 = D_3 + D_1 D_2' \\ &V = D_0 + D_1 + D_2 + D_3. \end{aligned}$$

Answer:

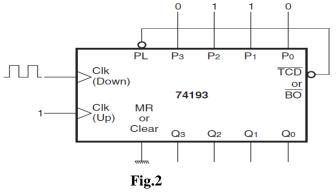

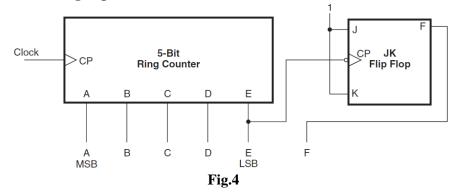

b. Refer to the logic circuit of Fig.3. Determine the modulus of this counter and write its counting sequence.

#### Answer:

| Clock pulse | Outputs |   |   |   |   |   |  |  |

|-------------|---------|---|---|---|---|---|--|--|

|             | A       | В | С | D | E | F |  |  |

| 1           | 1       | 0 | 0 | 0 | 0 | 0 |  |  |

| 2           | 0       | 1 | 0 | 0 | 0 | 0 |  |  |

| 3           | 0       | 0 | 1 | 0 | 0 | 0 |  |  |

| 4           | 0       | 0 | 0 | 1 | 0 | 0 |  |  |

| 5           | 0       | 0 | 0 | 0 | 1 | 0 |  |  |

| 6           | 1       | 0 | 0 | 0 | 0 | 1 |  |  |

| 7           | 0       | 1 | 0 | 0 | 0 | 1 |  |  |

| 8           | 0       | 0 | 1 | 0 | 0 | 1 |  |  |

| 9           | 0       | 0 | 0 | 1 | 0 | 1 |  |  |

| 10          | 0       | 0 | 0 | 0 | 1 | 1 |  |  |

| 11          | 1       | 0 | 0 | 0 | 0 | C |  |  |

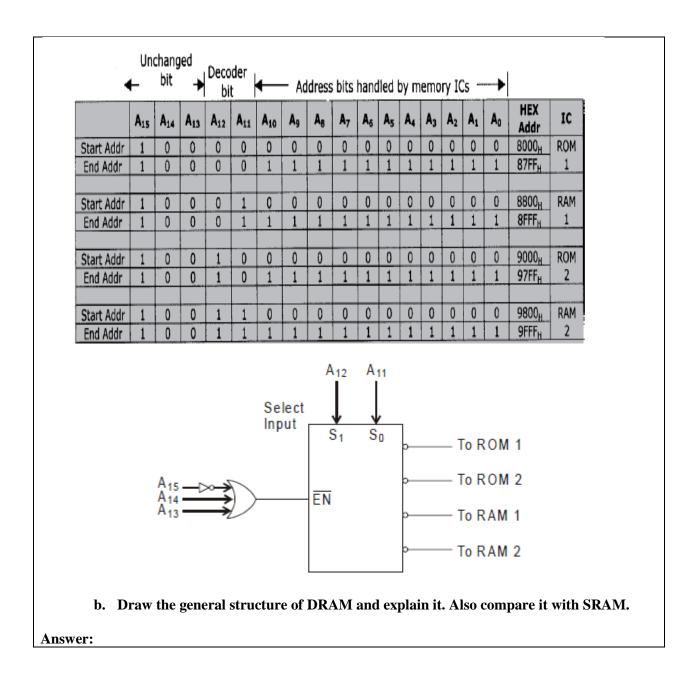

Q.9 a. It is required to obtain an 8K × 8 memory system for 8085 microprocessor system that has an addressing capability of 64K locations. Given memories are 2K × 8 ROM ICs and 2K × 8 RAM ICs. Obtain the exhaustive decoded system, which maps the 8K-memory system to begin from 8000H.

Answer:

# DE58/DC58 LOGIC DESIGN

© iete

**DEC 2014**

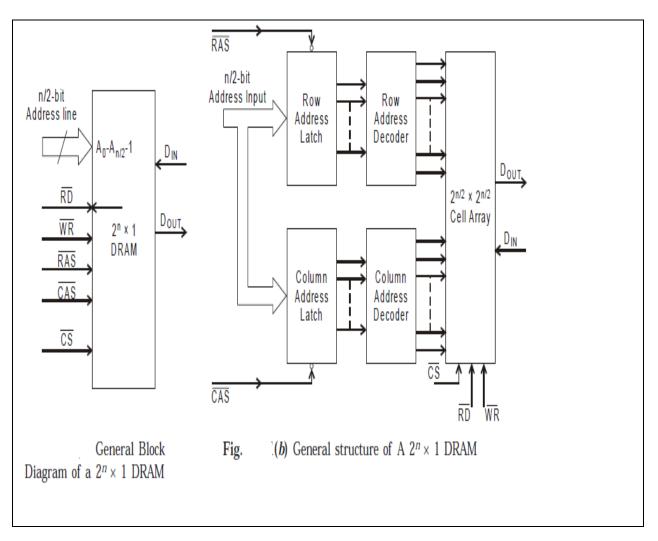

#### SRAMs and DRAMs

Having been studied the SRAMs & DRAMs it is worth to devote some time in comparative study of the two memories. Here are the few, which must be appreciated for the two types.

- The SRAMs cells can either be Bi-polar or MOS but DRAM cells can only be MOS.

- The DRAM cells are much simpler than the SRAM cells.

- SRAMs can retain information as long as power is ON where as DRAMs loose the retained information after a small time and thus requires refreshing.

- Data storage in DRAMs involves charge storage where as in SRAMs it involves ON/ OFF the transistors.

- DRAM cells can be constructed around a single transistor where SRAMs may require 11 transistors per cell. Thus DRAMs offer higher storage density. Infact the DRAMs are among the densest VLSI circuits in terms of transistor per chip. Due to this almost all the RAMs greater than 16KB are DRAMs.

- DRAMs are cost effective memory solution than the SRAMs.

- The actual read/write mechanism of DRAMs are much more tedious than that of SRAMs.

- DRAMs are always organized with the word length of 1-bit so that they are used with SIMM module where as SRAMs are organized for many different word lengths.

- DRAMs require many hardware pins so that address lines have be multiplexed where as it is seldom the case with SRAMs.

- Timing requirements of DRAMs are very complex as compared to the timing requirements of SRAMs.

- The DRAMs suffer from destructive read out so that each read must be followed by a write whereas there is no such problem with SRAMs.

- The DRAM requires extra hardware circuitry, called DRAM Controllers, for its proper operation where as SRAM does not need such supports.

- DRAMs are slower than the SRAMs due to destructive read out, address multiplexing and mainly due to refresh requirements.

- Future expansion of DRAM is easier as they are used with SIMM module in which case expansion involves replacement of board on the slot of main board. Needless to mention that using SIMM further increases the storage capacity than achieved by using a single DRAM chip.

- The DRAM cells offer lesser power consumption compared to either BJT or MOS SRAM cell.

## **Text Book**

1. Digital Systems – Principles and Applications, Ronald J Tocci, Neal S. Wildmer, Gregory L. Moss, Ninth Edition, Pearson Education, 2008