Code: DE58/DC58/DE108/DC108 Subject: LOGIC DESIGN

## **DiplETE - ET/CS (Current & New Scheme)**

PLEASE WRITE YOUR ROLL NO. AT THE SPACE PROVIDED ON EACH PAGE IMMEDIATELY AFTER RECEIVING THE QUESTION PAPER.

NOTE: There are 9 Questions in all.

• Question 1 is compulsory and carries 20 marks. Answer to Q.1 must be written in the space provided for it in the answer book supplied and nowhere else.

| <ul> <li>The answer sheet for the Q.1 will be collected by the invigilator after 45 minutes of the commencement of the examination.</li> <li>Out of the remaining EIGHT Questions answer any FIVE Questions. Each</li> </ul> |                                                                     |                                                               |               |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------|---------------|--|

| _                                                                                                                                                                                                                            | estion carries 16 marks.<br>y required data not explicitly          | given, may be suitably assumed and stated.                    |               |  |

| Q.1                                                                                                                                                                                                                          | Choose the correct or the b                                         | est alternative in the following:                             | $(2\times10)$ |  |

|                                                                                                                                                                                                                              | a. The Gray code for binary                                         | number 1101 is equivalent to                                  |               |  |

|                                                                                                                                                                                                                              | ( <b>A</b> ) 1101 ( <b>C</b> ) 0101                                 | ( <b>B</b> ) 1011 ( <b>D</b> ) 1110                           |               |  |

|                                                                                                                                                                                                                              | b. Output is high, when all in                                      | nput variables are high than logic gate is                    |               |  |

|                                                                                                                                                                                                                              | (A) AND<br>(C) NOT                                                  | ( <b>B</b> ) OR<br>( <b>D</b> ) EX-OR                         |               |  |

|                                                                                                                                                                                                                              | c. Result of adding $(01101)_B$ with $(01111)_B$ is                 |                                                               |               |  |

|                                                                                                                                                                                                                              | (A) 11010<br>(C) 11110                                              | ( <b>B</b> ) 10110 ( <b>D</b> ) 11100                         |               |  |

|                                                                                                                                                                                                                              | d. A decoder with 3 inputs can have a maximum of outputs.           |                                                               | ique          |  |

|                                                                                                                                                                                                                              | (A) 6<br>(C) 8                                                      | (B) 7<br>(D) 4                                                |               |  |

|                                                                                                                                                                                                                              | e. Which of the following is                                        | a sequential circuit:                                         |               |  |

|                                                                                                                                                                                                                              | <ul><li>(A) decoder</li><li>(C) counter</li></ul>                   | <ul><li>(B) multiplexer</li><li>(D) encoder</li></ul>         |               |  |

|                                                                                                                                                                                                                              | f. Master slave JK flip flop is used to avoid the following problem |                                                               |               |  |

|                                                                                                                                                                                                                              | <ul><li>(A) noise</li><li>(C) thermal run away</li></ul>            | <ul><li>(B) delay</li><li>(D) race - around problem</li></ul> |               |  |

| ROLL NO. |  |

|----------|--|

| NULL NU. |  |

**Subject: LOGIC DESIGN**

Code: DE58/DC58/DE108/DC108

g. A four bit synchronous counter is constructed using JK flip flop. The JK flip flop has propagation delay of 24 ns, the maximum frequency that can be used is given by

(**A**) 10.4 MHz

**(B)** 12.4 MHz

**(C)** 14.4 MHz

**(D)** 16.4 MHz

h. How many Flip-Flops are required for mod-16 counter?

**(A)** 16

**(B)** 12

(C) 8

**(D)** 4

i. The gates required to build a half adder are

- (A) XOR gate and NOR gate

- (B) XNOR gate and NOR gate

- (C) XOR gate and AND gate

- (D) XOR gate and NOT gate

j. How many address lines are required to access 4K Byte memory?

**(A)** 10

**(B)** 12

**(C)** 8

**(D)** 16

## Answer any FIVE Questions out of EIGHT Questions. Each question carries 16 marks.

**Q.2** a. Perform the following conversions:

**(8)**

- (i)  $(735)_8 = (?)_2$

- (ii)  $(37FD)_{16} = (?)_{10}$

- (iii)  $(37.45)_{10} = (?)_2$

- (iv) BCD number 1001001110000110 in to its decimal equivalent.

- b. Define binary system.

**(2)**

c. What are advantages and limitations of digital system over analog system? (6)

Q.3 a. What do you mean by universal gate? Implement AND, OR and NOT gate using any one of universal gate. (5)

b. Simplify the following expression, construct the corresponding logic circuit using basic gates. (6)

$$Y = A + \overline{B}C + ABC + A\overline{B}C$$

c. Draw the symbol of XNOR gate and explain its working with the help of truth table. (5)

## Code: DE58/DC58/DE108/DC108

**Subject: LOGIC DESIGN**

**Q.4** a. Perform the following operations:

**(8)**

**(8)**

- (i) Subtract -36 from 15 using 2's complement.

- (ii) Add 623 and 599 using BCD code.

- b. Design and explain full adder circuit using truth table.

- Q.5 a. Draw the circuit of 4 bit serial in serial out shift register and explain its working. (8)

- b. Explain design procedure to design synchronous counter whose state transition diagram is shown in **Fig.1**. (8)

Fig.1

- Q.6 a. What is decoder? Explain working of a 3 to 8 line decoder with the help of its detailed logic diagram and truth table. (8)

- b. What is multiplexer? Draw logic diagram of four inputs multiplexer and explain its working. (8)

- Q.7 a. Draw the logic diagram of JK flip flop and explain its working using truth table.

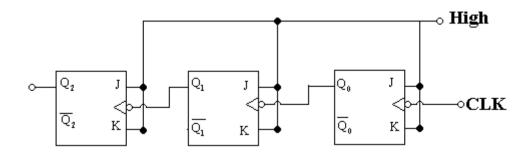

- b. Consider the circuit shown in **Fig.2**, (10)

- (i) Determine the counter's MOD number

- (ii) Determine the frequency at the output of the last FF (Q2) when the input clock frequency is 1MHz.

- (iii) What is the range of counting state for this counter?

- (iv) Assume starting state is 000. What will be the counter's state after 129 pulses?

Code: DE58/DC58/DE108/DC108

**Subject: LOGIC DESIGN**

(v) Draw waveforms at  $Q_0, Q_1, and, Q_2$  for the 10 input clock pulses.

Fig.2

- Q.8 a. Explain working principle of ripple counter with suitable logic diagram. (8)

- b. Design a mod 8 synchronous up/down counter and explain its working with the help of timing wave form. (8)

- Q.9 a. Explain with neat diagrams RAM architecture. (8)

- b. Describe CPU Memory connection with suitable block diagram. (8)