# **Diplete – ET (NEW SCHEME) – Code: DE56**

## Subject: ANALOG ELECTRONICS

**Time: 3 Hours**

**JUNE 2011**

Max. Marks: 100

$(2 \times 10)$

NOTE: There are 9 Questions in all.

- Question 1 is compulsory and carries 20 marks. Answer to Q.1 must be written in the space provided for it in the answer book supplied and nowhere else.

- The answer sheet for the Q.1 will be collected by the invigilator after 45 Minutes of the commencement of the examination.

- Out of the remaining EIGHT Questions answer any FIVE Questions. Each question carries 16 marks.

• Any required data not explicitly given, may be suitably assumed and stated.

#### **Q.1** Choose the correct or the best alternative in the following:

a. The CE amplifier circuits are preferred over CB amplifier circuits because they have

| (A) lower amplification factor       | ( <b>B</b> ) larger amplification factor |

|--------------------------------------|------------------------------------------|

| (C) high input and output resistance | ( <b>D</b> ) none of these               |

b. The input impedance of a JFET is \_\_\_\_\_ that of a ordinary transistor

| (A) equal     | (B) less than              |

|---------------|----------------------------|

| (C) more than | ( <b>D</b> ) none of these |

## c. A maximum efficiency of class-B amplifier is

| (A) 50 % | <b>(B)</b> 78.5 % |

|----------|-------------------|

| (C) 35 % | <b>(D)</b> 100 %  |

d. A non-inverting amplifier using op-amp employs the following type of feedback

| (A) voltage-shunt  | ( <b>B</b> ) current-shunt |

|--------------------|----------------------------|

| (C) current-series | <b>(D)</b> voltage series  |

e. The max frequency  $f_{max}$  at which we can obtain an undistorted output voltage of peak value  $V_m$  is given by

| (A) slew rate/ $6.28 \times V_{\rm m}$       | <b>(B)</b> $6.28 \times V_{\rm m}$ /slew rate |

|----------------------------------------------|-----------------------------------------------|

| (C) slew rate $\times 6.28$ / V <sub>m</sub> | <b>(D)</b> slew rate $\times V_m/6.28$        |

f. The instrumentation amplifier has an important feature of

| (A) high CMMR     | ( <b>B</b> ) low CMMR       |

|-------------------|-----------------------------|

| (C) low dc offset | ( <b>D</b> ) high dc offset |

g. LM 340 is a

| (A) positive regulator  | ( <b>B</b> ) negative regulator |

|-------------------------|---------------------------------|

| (C) include both ranges | ( <b>D</b> ) fixed regulator    |

h. If Differential gain  $A_d$  =3000 and Common Mode gain  $A_{cm}$  = 0.35 the CMMR is

| ( <b>A</b> ) 1225  | <b>(B)</b> 10000                          |

|--------------------|-------------------------------------------|

| ( <b>C</b> ) 80 dB | <b>(D)</b> Both <b>(B)</b> and <b>(C)</b> |

i. The CMOS Schmitt Trigger offers the advantage of

(A) low input impedance and low power consumption(B) high input impedance and high power consumption(C) high input impedance and low power consumption(D) low input impedance and high power consumption

j. The IC fabrication consist of four distinct layers, the layer no.1 is

| (A) thin n type material | <b>(B)</b> SiO $_2$ layer           |

|--------------------------|-------------------------------------|

| (C) aluminium layer      | <b>(D)</b> p type silicon substrate |

### Answer any FIVE Questions out of EIGHT Questions. Each question carries 16 marks.

| Q.2 | a. | List the basic processes used in the silicon planner technology, describe diffusion process in detail                                                                 | the<br>( <b>8</b> )  |

|-----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | b. | Compare the thin and thick film fabrication techniques                                                                                                                | (8)                  |

| Q.3 | a. | Draw an <b>h</b> parameter equivalent circuit for the CE unbypassed emitter b<br>configuration briefly explain the component of the model                             | oias<br>( <b>8</b> ) |

|     | b. | Given $I_E = 2.5 \text{mA}  h_{fe} = 140  h_{oe} = 20 \mu S(\mu \text{mho}) \text{ and } h_{ob} = 0.5 \mu S.$ Determ<br>the common emitter hybrid equivalent circuit. | ine<br>( <b>8</b> )  |

| Q.4 | a. | Describe the following terms<br>(i) Forward transfer admittance<br>(ii) Output admittance<br>(iii) Gate cutoff current<br>(iv) Breakdown voltage                      | (8)                  |

|     | b. | Determine the forward transfer admittance $Y_{fs}$ of a FET, when the dr current changes from 1mA to1.9 mA with a change in gate source voltation.                    |                      |

(8)

from -3.3V to -3 V.

- Q.5 a. Draw the circuit diagram of class B transformer coupled output stage of amplifier and explain its operation.(8)

- b. Describe the construction and working principle of liquid crystal cell. (8)

- Q.6 a. Describe the characteristics of an ideal op-amp, how an ideal amplifier drives an infinite number of other devices.(8)

- b. For an inverting amplifier, find the voltage gain  $v_0/v_s$  using characteristics of an ideal op-omp i.e the open loop voltage gain A<sub>OL</sub> is negatively infinite (8)

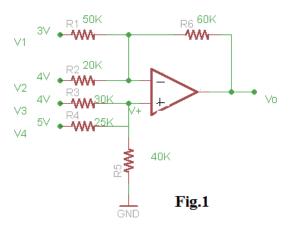

- **Q.7** a. Find  $V_0$  for the adder-subtractor circuit shown in Fig.1 (8)

- b. Draw and describe the operation of practical AC voltage follower circuit. (8)

- Q.8 a. Draw the circuit diagram of Phase shift oscillator and describe its operation.

- (8)

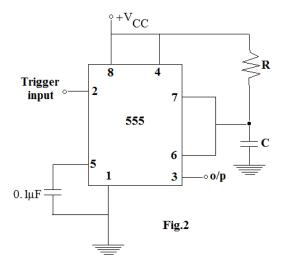

- b. For the monostable multivibrator circuit shown in Fig.2,  $R = 100K\Omega$  and the time delay T = 100 ms. Calculate the value of C. (8)

- Q.9 a. Describe the important performance parameters of series voltage regulator. List the value of each parameter as per data sheet of 7805. (8)

- b. Draw the functional diagram of the successive approximation ADC. Explain its operation. (8)