Code:

DE09 Subject:

DIGITAL ELECTRONICS

Code:

DE09 Subject:

DIGITAL ELECTRONICS

Time: 3 Hours Max. Marks: 100

NOTE: There are 9 Questions in all.

· Question 1 is compulsory and carries 20 marks. Answer to Q. 1. must be written in the space provided for it in the answer book supplied and nowhere else.

· Out of the remaining EIGHT Questions answer any FIVE Questions. Each question carries 16 marks.

· Any required data not explicitly given, may be suitably assumed and stated.

Q.1 Choose the correct or best alternative in the following: (2x10)

a. The decimal equivalent of binary number 11011 is

(A) 27 (B) 37

(C) 16 (D) 26

b. 1’s complement representation of decimal number –127 by using 8 bit representation is

(A) 11111111 (B) 10000000

(C) 01111111 (D) None of the above

c. Unused inputs on AND and NAND gates should be tied

(A) high (B) low

(C) tristated (D) None of the above

d. Which of following suffer from Electrostatic discharge

(A) TTL (B) CMOS

(C) DTL (D) RTL

e. The Gray code for binary number 10011 is

(A) 11010 (B) 00101

(C) 11011 (D) 11111

f. How many two input AND and two input OR gates will be required to realize Y=ABCD+BCD+E

(A) 5,3 (B) 5,2

(C) 5,4 (D) 8,2

g. How many address lines are required for 64K memory

(A) 16 (B) 15

(C) 14 (D) 6

h. Which of the following volatile memory

(A) PROM (B) EEPROM

(C) ROM (D) RAM

i. An 8 bit D/A converter has a step size of 6mV. The full scale output voltage is

(A) 1.53 V (B) 15.3 V

(C) 0.153V (D) None of the above

j. Which TTL logic gate is used for wired ANDing

(A) Tristate output (B) Totem pole

(C) ECL gates (D) Open Collector output

Answer any FIVE Questions out of EIGHT Questions.

Each question carries 16 marks.

Q.2 a. Convert

![]() to

decimal (6)

to

decimal (6)

b. Subtract 14 from 46 using 8 bit 2’s complement arithmetic (6)

c. Convert the excess-3 number 10011010 to its decimal equivalent (4)

Q.3 a. Show

that ![]() . (8)

. (8)

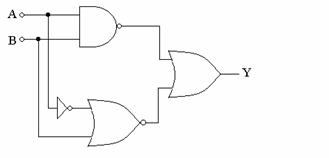

b. Find the Boolean expression for the circuit given below (8)

Q.4 a. Explain the operation of DTL NAND gate. (8)

b. Draw the K-map for the expression and reduce it

![]() (8)

(8)

Q.5 a. Implement the following function using a multiplexer

![]() (8)

(8)

b. Explain the operation of even and odd parity generator using logic diagram. (8)

Q.6 a. Draw the logic diagram of a full subtractor using half subtractors and explain its working with the help of a truth table. (8)

b. Explain the operation of master slave JK flip flop. (8)

Q.7 a. Draw and explain the operation of decade asynchronous counter. (8)

b. Give the circuit diagram of a 4-bit controlled left shift register and explain its working. (8)

Q.8 a. Explain the operation of successive operation A/D converter. (8)

b. Explain the following characteristics of DAC

(i) Gain (ii) Monotonocity

(iii) Speed (iv) Accuracy (8)

Q.9 a. How many 64x8 RAM chips are required to provide a memory of capacity 4096 bytes. How many lines of address bus must be used to access 4096 bytes of memory? How many lines of these will be common to each chip? How many bits must be decoded for chip select? What is size of decoder? (8)

b. Explain the operation of Dynamic RAM cell. List advantages of DRAMs. (8)