## Code: AC58/AT58 Subject: COMPUTER ORGANIZATION

## AMIETE - CS/IT (NEW SCHEME)

| Time: 3 Hours | DECEMBER 2011 | Max. Marks: 100 |

|---------------|---------------|-----------------|

|---------------|---------------|-----------------|

NOTE: There are 9 Questions in all.

- Please write your Roll No. at the space provided on each page immediately after receiving the Question Paper.

- Question 1 is compulsory and carries 20 marks. Answer to Q.1 must be written in the space provided for it in the answer book supplied and nowhere else.

- The answer sheet for the Q.1 will be collected by the invigilator after 45 Minutes of the commencement of the examination.

- Out of the remaining EIGHT Questions answer any FIVE Questions. Each question carries 16 marks.

- Any required data not explicitly given, may be suitably assumed and stated.

| Q.1 | Choose the corn | ect or the best | t alternative | in the | following: |

|-----|-----------------|-----------------|---------------|--------|------------|

|-----|-----------------|-----------------|---------------|--------|------------|

$(2\times10)$

- a. SPEC corresponds to

- (A) Signal Performance Evaluation Condition

- (B) Signed Processor Evaluation Condition

- (C) System Performance Evaluation Corporation

- (D) Saturated Processor Evaluation Condition

- b. The first byte of a 3 byte instruction will normally have

- (A) an operand or address

- (B) opcode

- **(C)** the address of memory

- **(D)** anyone of the above

- c. A memory has 16 bit address bus. The number of locations in the memory are

- (A) 65536

**(B)** 1024

**(C)** 16

- **(D)** 32

- d. 16 bytes are pulled from stack, having the top of stack address as 00CDH. What will be new top of the stack if on pushing into stack decrements top of stack and popping increments the top of stack?

- (A) 00ADH

(B) 00DDH

(C) 10CDH

- (**D**) 00BDH

- e. The number  $100110_2$  is numerically equal to

- **(A)**  $46_8$

**(B)**  $2A2_{H}$

**(C)** 36<sub>10</sub>

**(D)** 26<sub>10</sub>

## Code: AC58/AT58 Subject: COMPUTER ORGANIZATION

f. In a 4 bit carry look ahead adder, the addition process requires only (A) 3 gate delay **(B)** 1 XOR gate delay (C) 4 gate delay (D) 2 gate delay The basic performance equation for a computer is (A)  $T = \frac{S \times R}{N}$ **(B)**  $T = \frac{N \times R}{S}$ (C)  $T = \frac{N \times S}{R}$ **(D)**  $T = \frac{S \times R}{T}$ h. Fastest adder is (B) Serial adder (A) Ripple carry adder (C) Carry save adder (**D**) Carry look ahead adder In logical right shift operation, the fill in bits are always **(B)** 0 **(A)** 1 (C) sign bit must be repeated (D) MSB must be repeated j. Four memory chips of 16×4 size have their address buses connected together. This system will be of size **(A)**  $32 \times 8$ **(B)**  $256 \times 1$  $(C) 16 \times 16$ **(D)**  $64 \times 4$ Answer any FIVE Questions out of EIGHT Questions. Each question carries 16 marks. a. Explain in brief the evolution of computer generations. **(8)** b. A memory byte location contains the pattern 00101100. What does this pattern represent in (i) binary number (ii) An ASCII code. **(4)** c. Write short notes on big endian assignment. **(4)** a. Register R5 is used in a program to point to the top of a stack. Write a sequence of instructions using the index, auto increment and auto decrement addressing modes to program (i) Remove the top 10 items from the stack (ii) Copy the 5<sup>th</sup> item from the top into register R3. (4+4)b. Write short note on addressing modes. **(8)**

**Q.2**

Q.3

0.4

**(8)**

a. Explain any two methods of handling multiple I/O devices.

## Code: AC58/AT58 Subject: COMPUTER ORGANIZATION

b. Write short note on synchronous bus.

(8)

**Q.5** a. What is a port? What is the need of interfaces?

**(8)**

b. Briefly explain the working of SCSI bus.

**(8)**

**Q.6** a. Explain any two cache mapping functions.

- **(8)**

- b. What are the key factors that affect the performance and cost of a computer with respect to memory? Explain briefly. (8)

- Q.7 a. How many logic gates are needed to build the 4 bit carry look ahead adder?

Use the result of the above to calculate how many logic gates are needed to build 16 bit carry look ahead adder.

(4+4)

- b. Explain the various RAID levels.

**(8)**

**Q.8** a. Perform Booth's algorithm on the two signed 2's complement numbers:

A = 110011 (Multiplicand)

$$B = 101100 \text{ (Multiplier)}$$

(8)

b. Perform addition and subtraction on the given operands:

**(8)**

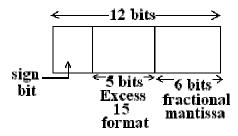

$$A = \begin{bmatrix} 0 & 10001 & 011011 \end{bmatrix}$$

$$B = \begin{bmatrix} 0 & 01111 & 101010 \end{bmatrix}$$

The format is:

- Q.9 a. Compare microprogrammed control vs hardwired control. (8)

- b. Briefly explain the steps required for execution of an instruction. (8)